Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

В первом поколении Serial ATA данные по кабелю передаются со скоростью 1500 Мбит/с, что с учетом кодирования 8B/10B обеспечивает скорость 150 Мбайт/с (без учета накладных расходов протоколов верхних уровней). В дальнейшем планируется повышать скорость передачи, и в интерфейсе заложена возможность согласования скоростей обмена по каждому интерфейсу в соответствии с возможностями хоста и устройства, а также качеством связи. Хост-адаптер имеет средства управления соединениями, программно эти средства доступны через специальные регистры Serial ATA.

В стандарте предусматривается управление энергорежимом интерфейсов. Каждый интерфейс кроме активного состояния может находиться в состояниях PARTIAL и SLUMBER с пониженным энергопотреблением, для выхода из которых требуется заметное время (10 мс).

Команды, требующие передачи данных, могут исполняться в различных режимах обмена. Обращение в режиме PIO и традиционный способ обмена по DMA (legacy DMA) выполняется аналогично привычному интерфейсу ATA. Однако внутренний протокол обмена между хост-адаптером и устройствами позволяет передавать между ними разноплановую информацию (структуры FIS определены не только для команд, состояния и собственно хранимых данных). В приложении D к спецификации описывается весьма своеобразный способ обмена по DMA, который предполагается основным (First-party DMA) для устройств Serial ATA. В традиционном контроллере DMA адаптера ATA для каждого канала имеется буфер, в который перед выполнением операции обмена загружают дескрипторы блоков памяти, участвующей в обмене (см. п. 9.2.1). Теперь же предполагается, что адресная информация, относящаяся к оперативной памяти хост компьютера, будет доводиться до устройства хранения , подключенного к адаптеру Serial ATA. Эта информация из устройства хранения при исполнении команд обмена выгружается в контроллер DMA хост-адаптера и используется им для формирования адреса текущей передачи. Мотивы и полезность этого нововведения не совсем понятны; расплатой за некоторое упрощение хост-адаптера (особенно многоканального) является усложнение протокола и расширение функций, выполняемых устройством хранения. Все-таки более привычно традиционное разделение функций, при котором задача устройств внешней памяти — хранить данные, «не интересуясь» тем, в каком месте оперативной памяти компьютера они должны находиться при операциях обмена.

Последовательный интерфейс ATA, как и его параллельный предшественник, предназначен для подключений устройств внутри компьютера. Длина кабелей не превышает 1 м, при этом все соединения радиальные, каждое устройство подключается к хост-адаптеру своим кабелем. В стандарте предусматривается и непосредственное подключение устройств к разъемам кросс-платы с возможностью «горячей» замены. Стандарт определяет новый однорядный двухсегментный разъем с механическими ключами, препятствующими ошибочному подключению. Сигнальный сегмент имеет 7 контактов (S1-S7), питающий — 15 (P1-Р15); все контакты расположены в один ряд с шагом 1,27 мм. Назначение контактов приведено в табл. 9.11. Малые размеры разъема (полная длина — около 36 мм) и малое количество цепей облегчают компоновку системных плат и карт расширения. Питающий сегмент может отсутствовать (устройство может получать питание и от обычного 4-контактного разъема ATA). Вид разъемов приведен на рис. 9.6. Для обеспечения «горячего» подключения контакты разъемов имеют разную длину, в первую очередь соединяются контакты «земли» Р4 и Р12, затем остальные «земли» и контакты предзаряда конденсаторов в цепях питания P3, Р7 и Р13 (для уменьшения броска потребляемого тока), после чего соединяются основные питающие контакты и сигнальные цепи.

Таблица 9.11. Разъем Serial ATA

| Контакт | Цепь | Назначение |

|---|---|---|

| S1 | GND | Экран |

| S2 | А+ | Дифференциальная пара сигналов А |

| S3 | А- | Дифференциальная пара сигналов А |

| S4 | GND | Экран |

| S5 | В- | Дифференциальная пара сигналов В |

| S6 | В+ | Дифференциальная пара сигналов В |

| S7 | GND | Экран |

| Ключи и свободное пространство | ||

| P1 | V33 | Питание 3,3 В |

| P2 | V33 | Питание 3,3 В |

| P3 | V33 | Питание 3,3 В, предзаряд |

| Р4 | GND | Общий |

| P5 | GND | Общий |

| P6 | GND | Общий |

| Р7 | V5 | Питание 5 В, предзаряд |

| Р8 | V5 | Питание 5 В |

| P9 | V5 | Питание 5 В |

| P10 | GND | Общий |

| Р11 | Резерв | |

| Р12 | GND | Общий |

| Р13 | V12 | Питание 12В, предзаряд |

| P14 | V12 | Питание 12 В |

| Р15 | V12 | Питание 12 В |

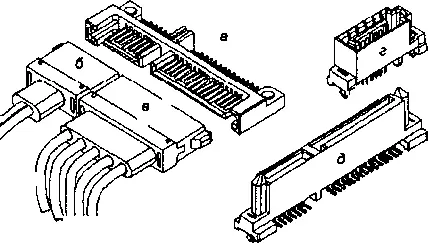

Рис. 9.6. Разъемы Serial ATA: a — полный разъем на устройстве, б — сигнальный сегмент кабельного разъема, в — питающий сегмент кабельного разъема, г — сигнальный сегмент разъема хост-адаптера, д — разъем хоста для непосредственного подключения устройства

Каждое устройство, подключенное к адаптеру Serial ATA, представляется тремя блоками регистров, два из которых соответствуют традиционным регистрам ATA (см. п. 9.2.1) и называются «теневыми», третий блок — новый. Привязка адресов блоков к адресному пространству хоста стандартом не регламентируется; для PCI-контроллера блоки задаются регистрами конфигурационного пространства и «теневые» регистры могут располагаться по стандартным адресам ATA.

В блоке управляющих регистров, как и в ATA, используется лишь один ( ASдля чтения, DCдля записи). В блоке командных регистров разрядность регистров SC, SN, CLи СНрасширена до 16 бит, назначение младших байтов сохранилось. В режиме LBA старшие байты регистров SN, CLи СНнесут биты логического адреса [24:31], [32:39] и [40:47] соответственно. В регистре D/Hбит DEVигнорируется (при эмуляции пар устройств на одном канале бит DEVиспользуется для выбора устройства). Из спецификации не совсем ясно, используются ли младшие биты D/Hдля задания бит LBA[27:24], поскольку эти же биты фигурируют в старшем байте SN.

Новый блок регистров SCR(Serial ATA Status and Control registers) состоит из 16 смежных 32-разрядных регистров SCR0- SCR15, из которых пока определены лишь 3 (остальные зарезервированы).

Регистр SStatus ( SCR0) — регистр текущего состояния интерфейса хост адаптера (только чтение).

♦ Биты [3:0] — поле DET, подключение устройств:

• 0000 — устройство не обнаружено, физической связи нет;

Читать дальшеИнтервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)