Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

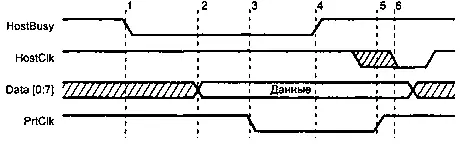

В этом режиме данные принимаются с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита CR.5=1. Как и предыдущие, режим является программно-управляемым — все сигналы квитирования анализируются и устанавливаются драйвером. Сигналы порта описаны в табл. 1.3, временные диаграммы — на рис. 1.2.

Таблица 1.3. Сигналы LPT-порта в байтном режима ввода-вывода

| Контакт | Сигнал SPP | Имя в байтном режиме | I/O | Бит | Описание |

|---|---|---|---|---|---|

| 1 | Strobe# | HostClk | O | CR.0\ | Импульс (низкого уровня) подтверждает прием байта в конце каждого цикла |

| 14 | AutoFeed# | HostBusy | О | CR.1\ | Сигнал квитирования. Низкий уровень означает готовность хоста принять байт; высокий уровень устанавливается по приему байта |

| 17 | SelectIn# | 1284Active | О | CR.3\ | Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

| 16 | Init# | Init# | O | CR.2 | Не используется; установлен высокий уровень |

| 10 | Ack# | PtrClk | I | SR.6 | Устанавливается в низкий уровень для индикации действительности данных на линиях Data[0:7]. В низкий уровень устанавливается в ответ на сигнал HostBusy |

| 11 | Busy | PtrBusy | I | SR.7\ | Состояние занятости прямого канала |

| 12 | PE | AckDataReq¹ | I | SR.5 | Устанавливается ПУ для указания на наличие обратного канала передачи |

| 13 | Select | Xflag¹ | I | SR.4 | Флаг расширяемости |

| 15 | Error# | DataAvail#¹ | I | SR.3 | Устанавливается ПУ для указания на наличие обратного канала передачи |

| 2-9 | Data[0:7] | Data[0:7] | I/O | DR[0:7] | Двунаправленный (прямой и обратный) канал данных |

¹ Сигналы действуют в последовательности согласования (см. ниже).

Рис. 1.2. Прием данных в байтном режиме

Фазы приема байта данных перечислены ниже.

1. Хост сигнализирует о готовности приема данных установкой низкого уровня на линии HostBusy.

2. ПУ в ответ помещает байт данных на линии Data[0:7].

3. ПУ сигнализирует о действительности байта установкой низкого уровня на линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

5. ПУ отвечает установкой высокого уровня на линии PtrClk.

6. Хост подтверждает прием байта импульсом HostClk.

Шаги 1–6 повторяются для каждого следующего байта. Квитирование осуществляется парой сигналов HostBusyи PtrClk; ПУ может и не использовать сигнал HostClk(это приглашение к выдаче следующего байта, напоминающее сигнал Ack# в интерфейсе Centronics). Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако он способен работать только на двунаправленных портах , которые раньше применялись в основном на малораспространенных машинах PS/2, но практически все современные порты можно сконфигурировать на двунаправленный режим (в настройках BIOS Setup — Bi-Diили PS/2).

1.3.3. Режим EPP

Протокол EPP (Enhanced Parallel Port — улучшенный параллельный порт) был разработан компаниями Intel, Xircom и Zenith Data Systems задолго до принятия стандарта IEEE 1284. Этот протокол предназначен для повышения производительности обмена по параллельному порту, впервые был реализован в чипсете Intel 386SL (микросхема 82360) и впоследствии принят множеством компаний как дополнительный протокол параллельного порта. Версии протокола, реализованные до принятия IEEE 1284, отличаются от нынешнего стандарта (см. ниже).

Протокол EPP обеспечивает четыре типа циклов обмена:

♦ запись данных;

♦ чтение данных;

♦ запись адреса;

♦ чтение адреса.

Назначение циклов записи и чтения данных очевидно. Адресные циклы используются для передачи адресной, канальной и управляющей информации. Циклы обмена данными отличаются от адресных циклов применяемыми стробирующими сигналами. Назначение сигналов порта EPP и их связь с сигналами SPP объясняются в табл. 1.4.

Таблица 1.4. Сигналы LPT-порта в режиме ввода-вывода EPP

| Контакт | Сигнал SPP | Имя в EPP | I/O | Описание |

|---|---|---|---|---|

| 1 | Strobe# | Write# | O | Низкий уровень — цикл записи, высокий — цикл чтения |

| 14 | AutoLF# | DataStb# | O | Строб данных. Низкий уровень устанавливается в циклах передачи данных |

| 17 | SelectIn# | AddrStb# | O | Строб адреса. Низкий уровень устанавливается в адресных циклах |

| 16 | Init# | Reset# | O | Сброс ПУ (низким уровнем) |

| 10 | Ack# | INTR# | I | Прерывание от ПУ |

| 11 | Busy | Wait# | I | Сигнал квитирования. Низкий уровень разрешает начало цикла (установку строба в низкий уровень), переход в высокий — разрешает завершение цикла (снятие строба) |

| 2-9 | Data[0:7] | AD[0:7] | I/O | Двунаправленная шина адреса/данных |

| 12 | PaperEnd | AckDataReq¹ | I | Используется по усмотрению разработчика периферии |

| 13 | Select | Xflag¹ | I | Используется по усмотрению разработчика периферии |

| 15 | Error# | DataAvail#¹ | I | Используется по усмотрению разработчика периферии |

¹ Сигналы действуют в последовательности согласования (см. ниже).

EPP-порт имеет расширенный набор регистров (табл. 1.5), который занимает в пространстве ввода-вывода 5–8 смежных байт.

Таблица 1.5. Регистры EPP-порта

| Имя регистра | Смещение | Режим | R/W | Описание |

|---|---|---|---|---|

| SPP Data Port | +0 | SPP/EPP | W | Регистр данных SPP |

| SPP Status Port | +1 | SPP/EPP | R | Регистр состояния SPP |

| SPP Control Port | +2 | SPP/EPP | W | Регистр управления SPP |

| EPP Address Port | +3 | EPP | R/W | Регистр адреса EPP . Чтение или запись в него генерирует связанный цикл чтения или записи адреса EPP |

| EPP Data Port | +4 | EPP | R/W | Регистр данных EPP . Чтение (запись) генерирует связанный цикл чтения (записи) данных EPP |

| Not Defined | +5…+7 | EPP | N/A | В некоторых контроллерах могут использоваться для 16-32-битных операций ввода-вывода |

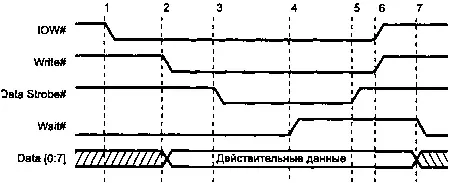

В отличие от программно-управляемых режимов, описанных выше, внешние сигналы EPP-порта для каждого цикла обмена формируются аппаратно по одной операции записи или чтения в регистр порта. На рис. 1.3 приведена диаграмма цикла записи данных, иллюстрирующая внешний цикл обмена, вложенный в цикл записи системной шины процессора (иногда эти циклы называют связанными). Адресный цикл записи отличается от цикла данных только стробом внешнего интерфейса.

Рис. 1.3. Цикл записи данных EPP

Читать дальшеИнтервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)