Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

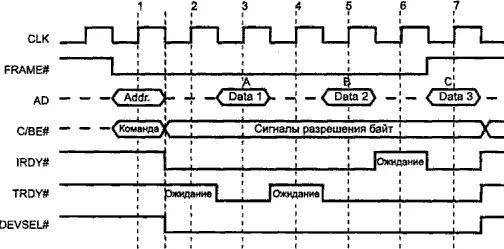

Для адреса и данных используются общие мультиплексированные линии AD. Четыре мультиплексированные линии С/BE[3:0]обеспечивают кодирование команд в фазе адреса и разрешения байт в фазе данных. В начале транзакции ведущее устройство активизирует сигнал FRAME#, по шине ADпередает целевой адрес, а по линиям С/BE#— информацию о типе транзакции (команде). Адресованное ЦУ отзывается сигналом DEVSEL#. Ведущее устройство указывает на свою готовность к обмену данными сигналом IRDY#, эта готовность может быть выставлена и раньше получения DEVSEL#. Когда к обмену данными будет готово и ЦУ, оно установит сигнал TRDY#. Данные по шине ADпередаются только при одновременном наличии сигналов IRDY#и TRDY#. С помощью этих сигналов ведущее устройство и ЦУ согласуют свои скорости, вводя такты ожидания. На рис. 6.7 приведена временная диаграмма обмена, в которой и ведущее устройство, и ЦУ вводят такты ожидания. Если бы они оба ввели сигналы готовности в конце фазы адреса и не снимали их до конца обмена, то в каждом такте после фазы адреса передавались бы по 32 бита данных, что обеспечило бы выход на предельную производительность обмена.

Рис. 6.7. Цикл обмена на шине PCI

Количество фаз данных в пакете явно не указывается, но перед последней фазой данных ведущее устройство при введенном сигнале IRDY#снимает сигнал FRAME#. В одиночных транзакциях сигнал FRAME#активен лишь один такт. Если устройство не поддерживает пакетные транзакции в ведомом режиме, то оно должно потребовать прекращения пакетной транзакции во время первой фазы данных (введя сигнал STOP#одновременно с TRDY#). В ответ на это ведущее устройство завершит данную транзакцию и продолжит обмен последующей транзакцией с новым значением адреса. После последней фазы данных ведущее устройство снимает сигнал IRDY#, и шина переходит в состояние покоя ( PCI Idle ) — оба сигнала FRAME#и IRDY#находятся в пассивном состоянии. Инициатор может начать следующую транзакцию и без такта покоя, введя FRAME#одновременно со снятием IRDY#. Такие быстрые смежные транзакции (Fast Back-to-Back) могут быть обращены как к одному, так и к разным ЦУ. Первый тип поддерживается всеми устройствами PCI, выступающими в роли ЦУ. На поддержку второго типа (она необязательна) указывает бит 7 регистра состояния (см. п. 6.2.12). Инициатору разрешают (если он умеет) использовать быстрые смежные транзакции с разными устройствами (битом 9 регистра команд), только если все агенты шины допускают быстрые обращения.

Шина позволяет уменьшить мощность (ток), потребляемую устройствами, ценой снижения производительности, применяя пошаговое переключение линий AD[31:0]и PAR(address/data stepping). Здесь возможны два варианта.

♦ Плавный шаг (continuous stepping) — начало формирования сигналов слабо точными формирователями за несколько тактов до введения сигнала-квалификатора действительной информации ( FRAME#в фазе адреса, IRDY#или TRDY#в фазе данных). За эти несколько тактов сигналы «доползут» до требуемого значения при меньшем токе.

♦ Дискретный шаг (diskrete stepping) — нормальные формирователи срабатывают не все сразу, а группами (например, побайтно), в каждом такте по группе. При этом снижаются броски тока, поскольку одновременно переключается меньше формирователей.

Устройство само может и не пользоваться этими возможностями (см. бит 7 регистра команд), но должно «понимать» такие циклы. Задерживая сигнал FRAME#, устройство рискует потерять право доступа к шине, если арбитр получит запрос от более приоритетного устройства.

Протокол квитирования обеспечивает надежность обмена — ведущее устройство всегда получает информацию об отработке транзакции ЦУ. Средством повышения надежности (достоверности) является применение контроля паритета: линии AD[31:0]и С/BE[3:0]#и в фазе адреса, и в фазе данных защищены битом паритета PAR(количество единичных бит этих линий, включая PAR, должно быть четным). Действительное значение PARпоявляется на шине с задержкой в один такт относительно линий AD и С/BE#. При обнаружении ошибки ЦУ вырабатывается сигнал PERR#(со сдвигом на такт после действительности бита паритета). В подсчете паритета при передаче данных учитываются все байты, включая и недействительные (отмеченные высоким уровнем сигнала С/ВЕх#). Состояние бит, даже и в недействительных байтах данных, во время фазы данных должно оставаться стабильным.

Каждая транзакция на шине должна быть завершена планово или прекращена, при этом шина должна перейти в состояние покоя (сигналы FRAME#и IRDY#пассивны). Завершение транзакции выполняется либо по инициативе ведущего устройства, либо по инициативе ПУ.

Ведущее устройство может завершить транзакцию одним из следующих способов.

♦ Нормальное завершение ( Completion ) выполняется по окончании обмена данными.

♦ Завершение по тайм-ауту ( Time-out ) происходит, когда во время транзакции у ведущего устройства отбирают право на управление шиной (снятием сигнала GNT#) и истекает время, указанное в его таймере Latency Timer. Это может случиться, если адресованное ЦУ оказалось непредвиденно медленным или запланирована слишком длинная транзакция. Короткие транзакции (с одной-двумя фазами данных) даже в случае снятия сигнала GNT#и срабатывания таймера завершаются нормально.

♦ Транзакция отвергается ( Master-Abort ), когда в течение заданного времени ведущее устройство не получает ответа ЦУ ( DEVSEL#).

Транзакция может быть прекращена по инициативе ЦУ ; для этого оно может ввести сигнал STOP#. Возможны три типа прекращения.

♦ Повтор ( Retry ) — сигнал STOP#вводится при пассивном сигнале TRDY#до первой фазы данных. Эта ситуация возникает, когда ЦУ из-за внутренней занятости не успевает выдать первые данные в положенный срок (16 тактов). Повтор является указанием ведущему устройству на необходимость нового запуска той же транзакции.

♦ Отключение ( Disconnect ) — сигнал STOP#вводится во время или после первой фазы данных. Если сигнал STOP#введен при активном сигнале TRDY#очередной фазы данных, то эти данные передаются и на том транзакция завершается. Если сигнал STOP#введен при пассивном сигнале TRDY#, то транзакция завершается без передачи данных очередной фазы. Отключение производится, когда ЦУ неспособно своевременно выдать или принять очередную порцию данных пакета.

♦ Отказ ( Target-Abor t) — сигнал STOP#вводится одновременно со снятием сигнала DEVSEL#(в предыдущих случаях во время появление сигнала STOP#сигнал DEVSEL#был активен). После этого данные уже не передаются. Отказ вводится, когда ЦУ обнаруживает фатальную ошибку или иные условия, по которым оно уже никак не сможет обслужить данный запрос.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)