Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей

- Название:OrCAD PSpice. Анализ электрических цепей

- Автор:

- Жанр:

- Издательство:ДМК Пресс, Питер

- Год:2008

- Город:Москва, Санкт-Петербург

- ISBN:978-5-9706-0009-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей краткое содержание

Это руководство по работе в программе OrCAD Pspice предназначено для всех, кто знаком с основными разделами электротехники. При постепенном усложнении задач объясняются все необходимые аспекты работы в OrCAD Pspice, что позволяет творчески применять их при дальнейшем анализе электрических и электронных схем и устройств. Рассмотрение материала начинается с анализа цепей постоянного тока, продолжается анализом цепей переменного тока, затем переходит к различным разделам полупроводниковой электроники. Информация изложена таким образом, чтобы каждый, кто изучал или изучает определенный раздел электротехники, мог сразу же использовать OrCAD Pspice на практике. Больше внимания, чем в других книгах по этой теме, уделяется созданию собственных моделей и использованию встроенных моделей схем в OrCAD Pspice.

На прилагаемом к книге DVD вы найдете демонстрационную версию программы OrCAD PSpice Student Edition 9, которой можно пользоваться свободно. Кроме того, на диске размещена версия OrCAD 10.5 Demo Release, с которой можно работать в течение 30 дней после установки на компьютер.

OrCAD PSpice. Анализ электрических цепей - читать онлайн бесплатно ознакомительный отрывок

Интервал:

Закладка:

20·lg(V(UI:OUT)/V(Vs:+)).

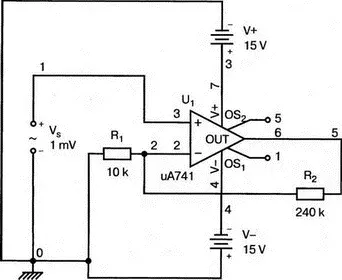

Рис. 16.14. Схема с ОУ uA741

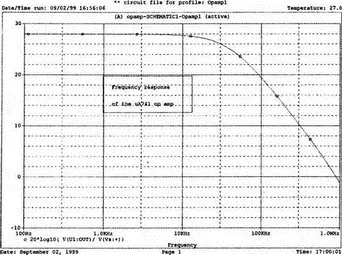

Результаты показаны на рис. 16.15. Сравните этот график с полученным в предыдущем примере при использовании собственной модели в Capture (рис. 16.9). Убедитесь, что коэффициент усиления на средней частоте равен 27,957 дБ.

Рис. 16.15. Частотная характеристика ОУ uA741

**** 09/02/99 17:27:56 *********** Evaluation PSpice (Nov 1998) **************

** circuit tile for profile: Opamp1

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.AC DEC 40 100Hz 1MegHz

.PROBE

*Netlist File: .INC "opamp-SCHEMATIC1.net"

* Alias File:

**** INCLUDING opamp-SCHEMATIC1.net ****

* source OPAMP

X_U1 1 2 3 4 5 uA741

R_R2 2 5 240k

R_R1 0 2 10k

V_V- 0 4 15V

V_V+ 3 0 15V

V_Vs 10 DC 0 V AC 1mV

**** RESUMING opamp-SCHEMATIC1-Opamp1.sim.cir ****

.INC "opamp-SCHEMATIC1.als"

**** INCLUDING opamp-SCHEMATIC1.als ****

.ALIASES

X_U1 U1(+=1 -=2 V+=3 V-=4 OUT=5 )

R_R2 R2(1=2 2=5 )

R_R1 R1(1=0 2=2 )

V_V- V-(+=0 -=4 )

V_V+ V+(+=3 -=0 )

V_Vs Vs(+=1 -=0 )

_ _(1=1)

_ _(5=5)

_ _(4=4)

_ _(2=2)

_ _(3=3)

.ENDALIASES

**** RESUMING opamp-SСНЕМАTIC-Opamp1.sim.cir ****

.END

**** Diode MODEL PARAMETERS

X_U1.dx

IS 800.000000E-18

RS 1

**** BJT MODEL PARAMETERS

X_U1.qx

NPN

IS 800.000000E-18

BF 93.75

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 20.64E-06 ( 3) 15.0000 ( 4) -15.0000

( 5) .0197 (X_U1.6) 26.12E-06 (X_U1.7) -.0780 (X_U1.8) -.0780

VOLTAGE SOURCE CURRENTS

NAME CURRENT

V_V- -1.667E-03

V_V+ -1.667E-03

V_Vs -7.972E-06

TOTAL POWER DISSIPATION 5.005-02 WATTS

Рис. 16.16. Выходной файл для схемы с ОУ uA741

Рассматривая выходной файл на рис. 16.16, обратите внимание на ссылку, касающуюся uA741 , в файле псевдонимов

X_U1 1 2 3 4 5 uA741

Необходимо отметить, что узлы от 1 до 5 — это узлы с номерами схемы, а не с теми, что помещены в условном обозначении uA741. Узлы 1 и 2 используются для неинвертирующего и инвертирующего входов, узлы 3 и 4 — для плюса и минуса источника постоянного напряжения соответственно, а узел 5 — для выхода. В конце командной строки приведен символ идентификации uA741. В списке псевдонимов мы находим

X_U1 U1(+=1 -=2 V+=3 V-=4 OUT=5)

Запись X обращается к подпрограмме, в которой описана модель для U 1, символы «плюс» и «минус» относятся к входным полюсам и так далее. На рис. 16.16 приведена лишь небольшая часть выходного файла, которая показывает, что в модель ОУ включены различные компоненты, такие как диоды, транзисторы и прочие.

Так как библиотечная модель для ОУ очень сложна, используйте ее только тогда, когда почувствуете, что более простая модель идеального ОУ (рис. 5.2, б) или модель для частотной характеристики (рис. 5.9) не могут обеспечить достаточной точности анализа.

Использование uA741 в качестве детектора уровня

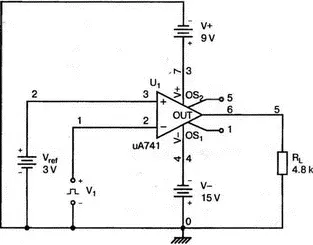

Схема на рис. 16.17 используется в качестве детектора уровня входного напряжения V 1. Создайте эту схему в Capture с именем leveldet. Используйте VPWL для V 1, VDC для V ref =3 В, V +=9 В и V –=9 В. Затем добавьте в схему резистор R L= 4,8 кОм и заземление. При двойном щелчке на символе V 1появляется окно (электронная таблица), в которое могут быть введены пары значений напряжение-время (до 10 пар). Так как более поздние времена и соответствующие им напряжения расположены слева, введем сначала V 6и T 6и продолжим, пока не введем все пары напряжения-времени. Значения должны быть следующими: (0V, 1s), (-3V, 0,8s), (-5V, 0,6s), (5V, 0,4s), (3V, 0,2s), (0V, 0s). Сохраните схему после введения всех компонентов и подготовьте PSpice-анализ с именем levels. Проведите анализ переходных процессов с шагом в 1 мс на интервале в 1 с.

Рис. 16.17. Схема детектора уровня

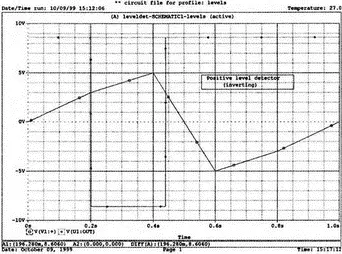

Проведите моделирование и получите в Probe графики как входного напряжения V(V1:+), так и выходного напряжения V(U1:OUT). Убедитесь, что график V 1следует за заданным графиком напряжения-времени. Графики, приведенные на рис. 16.18, показывают, что только до момента, когда входное напряжение достигает 3 В, выходное напряжение равно 8,6 В (немного меньше, чем V+= 9 В). Когда входное напряжение превышает 3 В, выходное напряжение понижается до -8,6 В и остается на этом уровне, пока входное напряжение не упадет ниже 3 В, затем процесс повторяется. Так как входное напряжение V i подается на инвертирующий вход ОУ, после достижения порогового напряжения V ref , выходное напряжение снижается.

Рис. 16.18. Входное и выходное напряжения для детектора уровня

**** 10/09/99 15:34:48 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: levels

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.TRAN 0 1s 0 1ms

.PROBE

*Netlist File:

.INC "leveldet-SCHEMATIC1.net"

*Alias Files

**** INCLUDING leveldet~SCHEMATIC1.net ****

* source LEVELDET

R_RL 5 0 4.8k

X_U1 2 1 3 4 5 uA741

V_V- 0 4 9V

V_V+ 3 0 9V

V_Vref 2 0 3V

V_V1 1 0

+PWL 0s 0V 0.2s 3V 0.4s 5V 0.6s -5V 0.8s -3V 1s 0V

**** RESUMING leveldet-SCHEMATIC1-levels.sim.cir ****

.INC "leveldet-SCHEMATIC1.als"

**** INCLUDING leveldet-SCHEMATICl.als ****

.ALIASES

R_RL RL(1=5 2=0 )

X_U1 U1(+=2 -=1 V+=3 V+=4 OUT=5 )

V_V- V-(+=0 -=4 )

V_V+ V+(+=3 -=0 )

V_Vref Vref(+=2 -=0 )

V_V1 V1(+=1 -=0 )

_ _(1=1)

_ _(2=2)

_ _(3=3)

_ _(4=4)

_ _(5=5)

.ENDALIASES

**** RESUMING leveldet-SCHEMATIC1-levels.sim.cir ****

.END

** circuit file for profile: levels **** Diode MODEL PARAMETERS

X_U1.dx

IS 800.000000E-18

RS 1

**** BJT MODEL PARAMETERS

X_U1.qx

NPN

IS 800.000000E-18

BF 93.75

**** INITIAL TRANSIENT SOLUTION TEMPERATURE = 27.000 DEG С

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 3.0000 ( 3) 9.0000 ( 4) -9.0000

( 5) 8.6136 (X_U1.6) -1.5163 (X_U1.7) 8.7041 (X_U1.8) 8.7041

VOLTAGE SOURCE CURRENTS

NAME CURRENT

V_V- -1.006E-03

V_V+ -9.903E-04

V_Vref -1.619E-07

V_V1 9.026E-12

TOTAL POWER DISSIPATION 1.80E-02 WATTS

Рис. 16.19. Выходной файл для детектора уровня

В выходном файле на рис. 16.19 приведена следующая командная строка:

V_V1 1 0

+PWL 0s 0V 0.2S 3V 0.4s 5V 0.6s -5V 0.8s -3V 1s 0V

Согласно этой записи V 1является кусочно-линейным (PWL) источником напряжения с парами время-напряжение, размещаемыми в нормальном порядке, то есть с начальными значениями времени и напряжения слева. При работе непосредственно в PSpice обычно используются круглые скобки, чтобы сгруппировать пару время-напряжение, хотя делать это не обязательно.

Читать дальшеИнтервал:

Закладка: