Коллектив Авторов - Цифровой журнал «Компьютерра» № 71

- Название:Цифровой журнал «Компьютерра» № 71

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:нет данных

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Коллектив Авторов - Цифровой журнал «Компьютерра» № 71 краткое содержание

Технология Gyricon: забытый электронный папирус Автор: Евгений Лебеденко, Mobi.ru

ТерралабПервый взгляд на Fedora Linux 15 Автор: Евгений Крестников

Путеводитель по настольным процессорам AMD (часть 1) Автор: Олег Нечай

Обзор ноутбука Eurocom W860CU Cougar Автор: Игорь Осколков

Путеводитель по настольным процессорам AMD (часть 2) Автор: Олег Нечай

КолумнистыВасилий Щепетнёв: Переход на летние деньги Автор: Василий Щепетнев

Кафедра Ваннаха: Цифровая шарага китайского образца Автор: Ваннах Михаил

Василий Щепетнёв: Приказано иметь честь Автор: Василий Щепетнев

Дмитрий Шабанов: Отпечатки пальцев и отпечатки мозга Автор: Дмитрий Шабанов

Кивино гнездо: На звон БитМонет Автор: Киви Берд

Кафедра Ваннаха: ТМО и парад геев Автор: Ваннах Михаил

На звон БитМонет (часть 2) Автор: Берд Киви

Василий Щепетнёв: Просить и не просить Автор: Василий Щепетнев

Кивино гнездо: Зачем вам думать? Автор: Киви Берд

Голубятня-ОнлайнГолубятня: Юбилейное откровение Автор: Сергей Голубицкий

Цифровой журнал «Компьютерра» № 71 - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

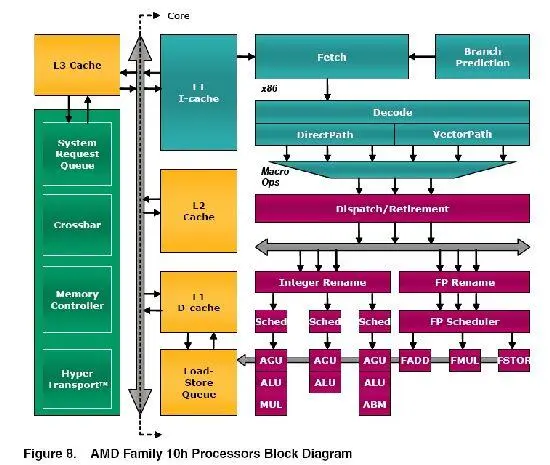

Архитектура AMD K10 достаточно хорошо известна, поэтому, не вдаваясь в подробности, напомним её характерные особенности. Прежде всего, это многоядерные чипы, в которых все ядра выполнены на одном кристалле, снабжены выделенным кэшем L2, а также общим для всех ядер кэшем L3 (за исключением Athlon II). Ядра претерпели существенные изменения по сравнению с K8: в частности, была переработана конструкция блоков выборки, предсказания переходов и ветвлений, диспетчеризации, что позволило оптимизировать загрузку ядра и в конечном итоге повысить производительность. Разрядность блоков SSE была повышена с 64 до 128 бит, появилась поддержка двух дополнительных инструкций SSE4a.

В процессорах реализована скоростная системная шина нового поколения HyperTransport 3.0, обеспечивающая пиковую скорость до 41,6 Гбайт/с в обоих направлениях в 32-битном режиме или до 10,4 Гбайт/с в одном направлении в 16-битном режиме и частотой до 2,6 ГГц. В силу избыточности такой пропускной способности для текущего конструктива в настоящее время применяется режим до 2 ГГц и 8,0 Гбайт/с.

Два независимых контроллера оперативной памяти DDR2-1066 (модели для разъёма AM2+ и AM3) или DDR3-1333 (чипы для разъёма AM3), встроенные в чип, обеспечивают ускоренный доступ к модулям.

В микропроцессорах с архитектурой K10 применяется комплексная система энергосбережения, состоящая из нескольких фирменных технологий — Cool’n’Quiet, CoolCore, Independent Dynamic Core и Dual Dynamic Power Management. Чипы способны автоматически снижать энергопотребление как всей микросхемы в целом, так и отдельных ядер и контроллера, а также отключать неиспользуемые элементы.

Технология Turbo Core, реализованная в четырёх- и шестиядерных Phenom II, обеспечивает автоматический динамический разгон наиболее загруженных ядер (от одного до двух или трёх) на частоту до 500 МГц выше номинальной. При этом частота менее нагруженных ядер снижается, поэтому даже в этом режиме не превышается заявленный термопакет.

Все чипы с архитектурой K10 производятся по 45-нм технологии, и по техпроцессу уступают современным процессорам Intel, которая начала массированный переход на 32-нм нормы ещё при запуске первых Nehalem. Самые мощные в линейке шестиядерные Phenom II X6 (Thuban), представленные весной 2010 года, также выпускаются по 45-нм технологии.

Процессоры семейств Athlon II и Phenom II рассчитаны на установку в разъём AM3, за исключением двух моделей: Phenom II X4 940 и 920, которые устанавливаются в Socket AM2+ и работают только с оперативной памятью DDR2. Чипы обеих линеек доступны в двух-, трёх- и четырёхъядерном исполнении (X2, X3, X4), «атлоны» также в одноядерном, а «феномы» — и в шестиядерном. Специально для энтузиастов разгона предлагаются модификации Black Edition, отличающиеся от стандартных моделей разблокированным множителем.

Микросхемы Athlon II X2 (Regor) представляют собой «настоящие» двуядерные чипы, а не четырёхъядерники Phenom II X4 (Deneb) с двумя нерабочими ядрами, как Phenom II X2 (Callisto). В свою очередь, Athlon II X3 — это Athlon II X4 c одним нефункциональным ядром, Phenom II X3 (Heka) — это Phenom II X4 (Deneb) с одним отключённым ядром, а Phenom II X4 (Zosma) — это Phenom II X6 (Thuban) с двумя отключёнными ядрами.

Каждое ядро Athlon II и Phenom II оснащается 128 Кбайт кэш-памяти L1 и 512 Кбайт кэша второго уровня. Однако, в отличие от Phenom II, у «атлонов» нет общей кэш-памяти L3, поэтому они чаще обращаются к заведомо более медленной системной памяти. Результат — ограниченная производительность в ресурсоёмких приложениях, в частности, в трёхмерной графике и компьютерных играх. Впрочем, в сочетании с хорошей дискретной видеокартой системы на Athlon II демонстрируют вполне достойную игровую производительность.

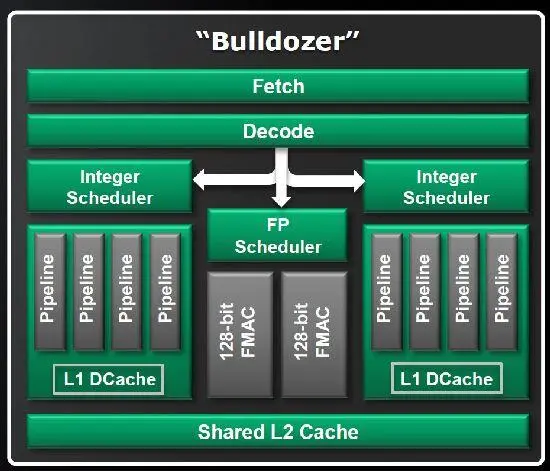

Процессоры на основе микроархитектуры следующего поколения под кодовым названием Bulldozer должны появиться на рынке в самое ближайшее время — в июне 2011 года. Эти чипы представляют собой одну из реализаций всё более популярной концепции «системы на чипе», когда на одном кристалле размещаются несколько вычислительных ядер, графические ядра и различные контроллеры, ранее входившие в состав наборов логики. В компании AMD разработкой гибридного процессора модульного типа под названием Fusion занялись ещё в 2006 году, сразу после покупки канадского производителя графических чипов ATI Technologies. Однако если Intel уже несколько лет массово выпускает ЦП со встроенной графикой, AMD так и не представила серийной десктопной модели — по некоторым сведениям, из-за проблем с производством. При этом если первоначально Fusion планировалось выпускать по 45-нм технологии, то Bulldozer уже рассчитаны на 32-нм техпроцесс.

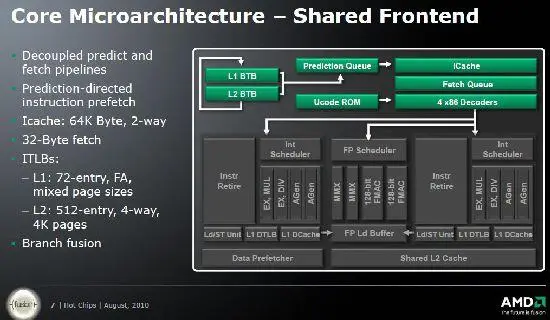

Процессоры следующего поколения будут состоять из одного или нескольких двухъядерных модулей с общим внешним интерфейсом (блоков выборки и декодирования), блоком вычислений с плавающей запятой и кэш-памятью второго уровня. Поскольку в работающем многоядерном процессоре некоторые блоки часто остаются незадействованными, их можно сделать общими для нескольких ядер. В результате процессор будет состоять из меньшего числа блоков и его физические размеры будут меньше. Это сделает его экономичнее, «прохладнее» и, разумеется, дешевле. При этом по производительности в реальных приложениях такой чип не будет уступать микросхеме с «полноценными» ядрами.

Микроархитектура Bulldozer совместима со стандартными инструкциями x86 и поддерживает дополнительные наборы инструкций SSE4.1, SSE4.2, AVX, AES и LWP. Набор векторных инструкций AVX (Advanced Vector Extensions) был разработан в Intel в качестве возможного набора мультимедийных инструкций SSE5 нового поколения, и он уже используется в процессорах Core на основе архитектуры Sandy Bridge. В чипах Bulldozer этот набор дополнен двумя проприетарными расширениями XOP и FMA4. Инструкции AES (Advanced Encryption Standard) отвечают за поддержку алгоритмов шифрования, а LWP (Light Weight Profiling) позволяют одним программам отслеживать производительность других, что особенно важно при отладке софта. Иными словами, в Bulldozer поддерживаются практически любые когда-либо написанные инструкции для x86-совместимых процессоров.

Блок выборки, общий для пары ядер, отвечает за отбор и передачу на декодирование следующей инструкции из кэш-памяти или оперативной памяти. Кэш инструкций первого уровня, как неотъемлемая часть блока выборки, также общий для всего модуля, при этом у каждого «ядра» есть выделенный кэш данных L1. В чипа предусмотрена также общая кэш-память второго уровня для двух «ядер» и кэш третьего уровня, общий для всех «ядер» и двухъядерных модулей.

Читать дальшеИнтервал:

Закладка: