Стивен Барретт - Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С

- Название:Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С

- Автор:

- Жанр:

- Издательство:Издательский дом «ДМК-пресс»

- Год:2007

- Город:Москва

- ISBN:5-9706-0034-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Стивен Барретт - Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С краткое содержание

В книге последовательно рассматриваются все этапы создания встраиваемых систем на микроконтроллерах с применением современных технологий проектирования. Задумав эту книгу, авторы поставили перед собой задачу научить читателя искусству создания реальных устройств управления на однокристальных микроконтроллерах.

Издание содержит материал, охватывающий все вопросы проектирования, включает множество заданий для самостоятельной работы, примеры программирования, примеры аппаратных решений и эксперименты по исследованию работы различных подсистем микроконтроллеров.

Данная книга является прекрасным учебным пособием для студентов старших курсов технических университетов, которые предполагают связать свою профессиональную деятельность с проектированием и внедрением встраиваемых микропроцессорных систем. Книга также будет полезна разработчикам радиоэлектронной аппаратуры на микроконтроллерах.

Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

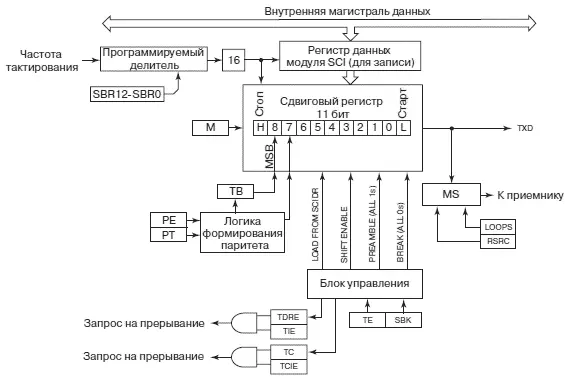

Рис. 4.60.Аппаратные средства блока передатчика в составе контроллера асинхронного обмена

Аппаратные средства передатчика модуля SCI в составе МК 68HC12 предусматривают возможность автоматического (без специальных команд программы) формирования бита паритета по содержимому передаваемого слова данных.

Блок управления формирует все необходимые сигналы для корректной работы аппаратных средств передатчика. Работа передатчика разрешается независимо от состояния приемника в составе этого же контроллера SCI. Если бит TE в регистре управления установлен, то работа передатчика активизируется, и соответствующий вывод порта PORT S конфигурируется как выход TxD. Блок управления также генерирует все запросы на прерывания, связанные с работой передатчика.

Скорость передачи данных определяется программируемым делителем, на вход которого поступает импульсная последовательность P_CLOCK системы тактирования МК. Коэффициент деления назначается битами SBR12…SBR0 регистра скорости обмена.

Байт данных, подлежащий передаче, должен быть записан с использованием любой команды пересылки в регистр данных контроллера SCI. Если сдвиговый регистр в момент записи не занят, то байт данных будет автоматически перемещен из регистра данных в сдвиговый регистр. При этом бит паритета, стартовый и стоповый биты будут подставлены автоматически. Далее без дополнительных команд программы управления начнется передача сформированного в сдвиговом регистре кадра обмена на выход TxD.

4.18.2. Приемник контроллера SCI

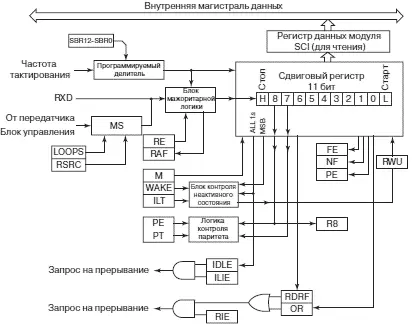

Функциональная схема приемника в составе контроллера SCI представлена на рис. 4.61. Так же, как и в приемнике, основным ее элементом является 11-разрядный сдвиговый регистр. Однако это уже собственный регистр приемника, поскольку контроллер SCI обеспечивает возможность обмена в двух направлениях одновременно. Напротив, программируемый делитель является общим для приемника и передатчика. Поэтому скорость приема и передачи данных для одного и того же контроллера SCI всегда одинакова.

Рис. 4.61.Аппаратные средства блока приемника в составе контроллера асинхронного обмена

Работа приемника разрешается установкой бита PE в регистре управления. Если приемник активирован, то соответствующая линия порта PORT S конфигурируется как вход RxD. Блок мажоритарной логики обрабатывает входной сигнал и формирует очередной младший бит сдвигового регистра приемника. В процессе приема каждый поступающий бит опрашивается три раза. Если все три выборки совпали (три 1 или три 0), то соответствующее значение передается в сдвиговый регистр. При несовпадении (два бита равны 1, третий — 0, или наоборот) значение бита формируется по логике «два из трех». Но одновременно устанавливается бит наличия шума на линии NF.

По завершении приема всех 10 или 11 бит кадра приемник автоматически переписывает принятую информацию в регистр данных контроллера SCI и устанавливает в 1 флаг RDRF, который информирует МК о необходимости считывания принятого байта в память МК.

4.18.3. Регистры контроллера SCI

Контроллер асинхронного обмена обслуживается несколькими группами регистров специальных функций:

• Регистры скорости обмена;

• Регистры управления;

• Регистры состояния;

• Регистры данных.

Далее мы рассмотрим формат и назначение битов каждого регистра модуля SCI.

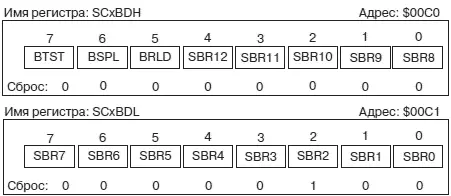

Два 8-разрядных регистра SCxBDH и SCxBDL предназначены для управления скоростью обмена по последовательному интерфейсу SCI. Для назначения желаемой скорости используются разряды SBR12…SBR0 этих двух регистров (рис. 4.63). Число, которое следует записать в эти разряды может быть определено с использованием таблицы рис. 4.62 или рассчитано по формуле:

SBR = PCLOCK/(16×BAUD_RATE),

где SBR — десятичный эквивалент двоичного кода, который должен быть записан в разряды SBR12…SBR0 регистров SCxBDH и SCxBDL, PCLOCK — частота импульсной последовательности PCLK в Герцах, BAUD_RATE — частота обмена в бодах.

| Желаемая скорость обмена (бод) | Значение коэффициента при частоте внутренней системной шины | |

|---|---|---|

| 4 МГц | 8 МГц | |

| 110 | 2273 | 4545 |

| 300 | 833 | 1667 |

| 600 | 417 | 833 |

| 1200 | 208 | 417 |

| 2400 | 104 | 208 |

| 4800 | 52 | 104 |

| 9600 | 26 | 52 |

| 14400 | 17 | 35 |

| 19200 | 13 | 26 |

| 38400 | — | 13 |

Рис. 4.62.Выбор коэффициента деления модуля SCI

Рис. 4.63.Формат регистра скорости обмена SCxBDH/SCxBDL

Необходимо настроить первый контроллер асинхронного обмена (SCI0) на скорость 9600 бод. Если частота импульсной последовательности PCLK равна 8 МГц, то коэффициент деления, который должен быть записан в регистры SC0BDH и SC0BDL, равен:

SBR0 = 8000000/(16×9600) = 52 = $34

Следующий программный фрагмент реализует инициализацию скорости обмена:

/*----------------------*/

/* filename: ini_SCI0.c */

/*----------------------*/

#include <912b32.h>

void main(void) {

SC0BDH = 0х00;

SC0BDL = 0х34;

}

/*----------------------*/

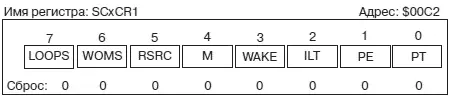

Рис. 4.64.Формат регистра управления SCxCR1

Формат первого регистра управления контроллера SCI представлен на рис. 4.64. Биты этого регистра имеет следующее назначение:

LOOPS:

Бит разрешения «замкнутого» режима работы контроллера SCI. Установка в 1 бита LOOPS вызывает перекоммутацию входа приемника линии RxD, который внутренними средствами отсоединяется от вывода RxD и подсоединяется к выходу передатчика. В этом режиме возможен контроль передаваемой информации. Также режим может быть использован для тестирования работы программного обеспечения без использования устройства управления верхнего уровня. Для реализации «замкнутого» режима должна быть разрешена работа как передатчика, так и приемника.

1 — «замкнутый» режим работы разрешен;

0 — «замкнутый» режим работы запрещен.

WOMS:

Бит выбора режима открытого коллектора. Этот бит определяет состояние выходных буферов линий TxD и RxD.

1 — буферы переведены в режим открытого коллекторного выхода;

0 — буферы работают в режиме обычного двухстабильного логического выхода (TxD) и входа (RxD).

Читать дальшеИнтервал:

Закладка: