Эрл Гейтс - Введение в электронику

- Название:Введение в электронику

- Автор:

- Жанр:

- Издательство:Феникс

- Год:1998

- Город:Ростов-на-Дону

- ISBN:5-222-00417-1

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Эрл Гейтс - Введение в электронику краткое содержание

Введение в электронику - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Механическое переключение не может удовлетворительно выполнить эту задачу. Следовательно, мультиплексоры, используемые для выполнения высокоскоростного переключения, должны состоять из электронных компонентов.

Мультиплексоры имеют дело с данными двух типов: аналоговыми и цифровыми. Мультиплексоры для аналоговых сигналов состоят из реле и транзисторных ключей.

Мультиплексоры для цифровых сигналов состоят из стандартных логических элементов.

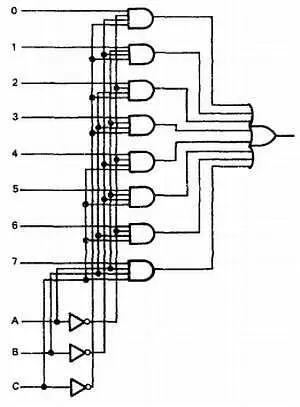

Цифровые мультиплексоры позволяют направлять цифровые данные от отдельных источников в общую линию для передачи по назначению. Типичный мультиплексор имеет несколько входов и один выход. Входы мультиплексора активируются входом выбора данных, определяющих вход, по которому данные будут приниматься. На рис. 35–13 изображена логическая схема восьмивходового мультиплексора. Заметим, что мультиплексор имеет три линии управления входами, обозначенные А, В и С . Путем подачи соответствующего двоичного кода на линии управления, может быть выбран любой из восьми входов.

Рис. 35–13. Логическая схема восьмивходового мультиплексора.

Обозначение цифрового мультиплексора показано на рис. 35–14.

Рис. 35–14. Логическое обозначение восьмивходового мультиплексора.

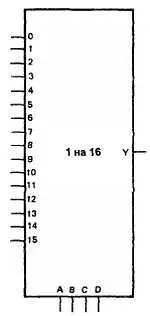

На рис. 35–15 изображено обозначение 16-входового мультиплексора. Заметим, что мультиплексор имеет четыре линии управления для активации шестнадцати входов данных.

Рис. 35–15. Логическое обозначение шестнадцативходового мультиплексора.

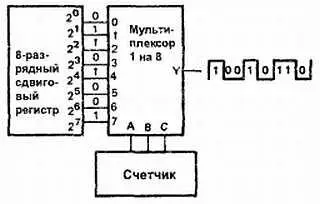

Кроме селекции потоков данных, мультиплексоры широко используются для преобразования данных из параллельного кода в последовательный. Двоичное слово, представленное параллельным кодом, подается на вход мультиплексора. Подавая на управляющие входы последовательность разрешающих кодов, можно получить на выходе последовательное представление параллельного двоичного слова, поданного на вход.

На рис. 35–16 изображена схема преобразования данных из параллельного кода в последовательный с помощью мультиплексора. Трехразрядное двоичное слово со счетчика используется для выбора нужного входа. Параллельное восьмиразрядное слово подается на вход мультиплексора.

При увеличении двоичного числа на выходе счетчика последовательно выбираются входы мультиплексора. На выходе мультиплексора появляется последовательное двоичное слово, равное параллельному, поданному на вход.

Рис. 35–16. Использование мультиплексора для преобразования данных, представленных параллельным кодом, в последовательный.

35-3. Вопросы

1. Что такое мультиплексор?

2. Как используются мультиплексоры?

3. Нарисуйте логическую схему мультиплексора?

4. С данными каких типов имеют дело мультиплексоры?

5. Как использовать мультиплексор для преобразования данных из параллельного кода в последовательный?

Сумматор

Сумматор — это главный вычислительный элемент цифрового компьютера. Компьютер выполняет всего несколько подпрограмм, в которых не используется сумматор. Сумматоры рассчитаны на работу либо в параллельных, либо в последовательных цепях. Поскольку параллельный сумматор работает быстрее и используется чаще, он будет рассмотрен более детально.

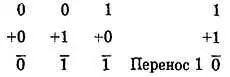

Для того чтобы понять, как работает сумматор, необходимо вспомнить правила сложения:

На рис. 35–17 изображена таблица истинности, основанная на этих правилах. Заметим, что греческая буква сигма ( Σ ) используется для обозначения суммы столбца. Столбец переноса обозначен С 0. Эти обозначения используются в промышленности при описании сумматора.

Рис. 35–17. Таблица истинности, составленная с помощью правил сложения.

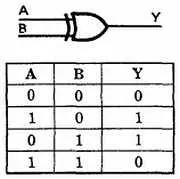

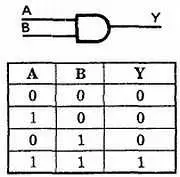

Столбец суммы в таблице истинности совпадает со столбцом выхода в таблице истинности для элемента исключающее ИЛИ (рис. 35–18). Столбец переноса совпадает со столбцом выхода в таблице истинности для элемента И (рис. 35–19).

Рис. 35–18. Таблица истинности для элемента исключающее ИЛИ.

Рис. 35–19. Таблица истинности для элемента И.

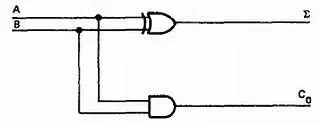

На рис. 35–20 изображены элементы И и исключающее ИЛИ, соединенные параллельно для того, чтобы обеспечить логическую функцию, необходимую для одноразрядного сложения. Выход переноса ( С 0) обеспечивается элементом И, а выход суммы ( Σ ) обеспечивается элементом исключающее ИЛИ. Входы А и В соединены со входами элемента И и элемента исключающее ИЛИ. Таблица истинности для этой цепи такая же, как и таблица истинности, полученная с использованием правил двоичного сложения (рис. 35–17).

Рис. 35–20. Схема полусумматора.

Поскольку эта цепь не учитывает какие-либо переносы, она называется полусумматором. Он может быть использован в качестве сумматора младшего разряда при сложении двоичных чисел.

Сумматор, учитывающий перенос, называется полным сумматором. Полный сумматор имеет три входа и выходы для суммы и переноса. На рис. 35–21 приведена таблица истинности для полного сумматора. Вход C 1— это вход переноса. Выход С 0— это выход переноса.

Рис. 35–21. Таблица истинности для полного сумматора.

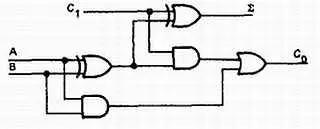

На рис. 35–22 изображен полный сумматор, составленный из двух полусумматоров. Выходы обоих полусумматоров поданы на входы элемента ИЛИ для получения выхода переноса. На выходе переноса будет 1, если на обоих входах либо первого, либо второго элемента исключающее ИЛИ также будут высокие уровни. На рис. 35–23 показаны обозначения полусумматора и полного сумматора.

Рис. 35–22. Логическая схема полного сумматора, использующая два полусумматора.

Читать дальшеИнтервал:

Закладка: