Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

♦ ECR.3— DMAEN— (DMA Enable) разрешает обмен по каналу DMA;

♦ ECR.2— SERVICEINTR— (Service Interrupt) запрещает сервисные прерывания, которые вырабатываются по окончании цикла DMA (если он разрешен), по порогу заполнения/опустошения FIFO-буфера (если не используется DMA) и по ошибке переполнения буфера сверху или снизу;

♦ ECR.1— FIFOFS— (FIFO Full Status) сигнализирует о заполнении буфера; при FIFOFS=1 в буфере нет ни одного свободного байта;

♦ ECR.0— FIFOES— (FIFO Empty Status) указывает на полное опустошение буфера; комбинация FIFOFS= FIFOES=1 означает ошибку работы с FIFO (переполнение сверху или снизу).

Когда порт находится в стандартном или двунаправленном режимах (000 или 001), первые три регистра полностью совпадают с регистрами стандартного порта. Так обеспечивается совместимость драйвера со старыми адаптерами и старых драйверов с новыми адаптерами.

По интерфейсу с программой ECP-порт напоминает EPP: после установки режима (записи кода в регистр ECR) обмен данными с устройством сводится к чтению или записи в соответствующие регистры. За состоянием FIFO-буфера наблюдают либо по регистру ECR, либо по обслуживанию сервисных прерываний от порта. Весь протокол квитирования генерируется адаптером аппаратно. Обмен данными с ЕСР-портом (кроме явного программного) возможен и по прямому доступу к памяти (каналу DMA), что эффективно при передаче больших блоков данных.

1.3.6. Согласование режимов IEEE 1284

ПУ в стандарте IEEE 1284 обычно не требуют от контроллера реализации всех предусмотренных этим стандартом режимов. Для определения режимов и методов управления конкретным устройством стандарт предусматривает последовательность согласования ( negotiation sequence ). Последовательность построена так, что старые устройства, не поддерживающие IEEE 1284, на нее не ответят, и контроллер останется в стандартном режиме. Периферия IEEE 1284 может сообщить о своих возможностях, и контроллер установит режим, удовлетворяющий и хост, и ПУ.

Во время фазы согласования контроллер выставляет на линии данных байт расширяемости ( extensibility byte ), запрашивая подтверждение на перевод интерфейса в требуемый режим или прием идентификатора ПУ (табл. 1.9). Идентификатор передается контроллеру в запрошенном режиме (любой режим обратного канала, кроме EPP). ПУ использует сигнал Xflag( Selectв терминах SPP) для подтверждения запрошенного режима обратного канала, кроме полубайтного, который поддерживается всеми устройствами IEEE 1284. Бит Extensibility Link requestпослужит для определения дополнительных режимов в будущих расширениях стандарта.

Таблица 1.9. Биты в байте расширяемости

| Бит | Описание | Допустимые комбинации бит [7:0] |

|---|---|---|

| 7 | Request Extensibility Link — зарезервирован | 1000 0000 |

| 6 | Запрос режима ЕРР | 0100 0000 |

| 5 | Запрос режима ЕСР с RLE | 0011 0000 |

| 4 | Запрос режима ЕСР без RLE | 0001 0000 |

| 3 | Зарезервировано | 0000 1000 |

| 2 | Запрос идентификатора устройства с ответом в режиме: | |

| полубайтный | 0000 0100 | |

| байтный | 0000 0101 | |

| ЕСР без RLE | 0001 0100 | |

| ЕСР с RLE | 0011 0100 | |

| 1 | Зарезервировано | 0000 0010 |

| 0 | Запрос полубайтного режима | 0000 0001 |

| none | Запрос байтного режима | 0000 0000 |

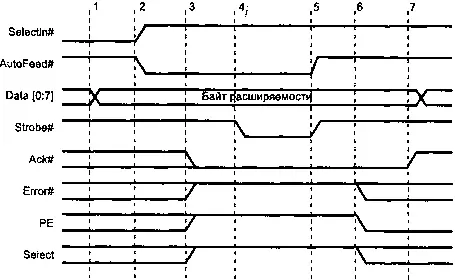

Последовательность согласования (рис. 1.6) состоит из следующих шагов.

1. Хост выводит байт расширяемости на линии данных.

2. Хост устанавливает высокий уровень сигнала SelectIn#и низкий — AutoFeed#, что означает начало последовательности согласования.

3. ПУ отвечает установкой низкого уровня сигнала Ack#и высокого — Error#, PaperEndи Select. Устройство, «не понимающее» стандарта 1284, ответа не даст, и дальнейшие шаги не выполнятся.

4. Хост устанавливает низкий уровень сигнала Strobe#для записи байта расширяемости в ПУ.

5. Хост устанавливает высокий уровень сигналов Strobe#и AutoLF#.

6. ПУ отвечает установкой в низкий уровень сигналов PaperEndи Error#, если ПУ имеет обратный канал передачи данных. Если запрошенный режим поддерживается устройством, на линии Selectустанавливается высокий уровень, если не поддерживается — низкий.

7. ПУ устанавливает высокий уровень на линии Ack#для указания на завершение последовательности согласования, после чего контроллер задает требуемый режим работы.

Рис. 1.6.Последовательность согласования режимов IEEE 1284

1.3.7. Физический и электрический интерфейсы

Стандарт IEEE 1284 определяет физические характеристики приемников и передатчиков сигналов, которые по уровням совместимы с ТТЛ. Спецификации стандартного порта не задавали типов выходных схем, предельных значений величин нагрузочных резисторов и емкости, вносимой цепями и проводниками. На относительно невысоких скоростях обмена разброс этих параметров не вызывал проблем совместимости. Однако расширенные (функционально и по скорости передачи) режимы требуют четких спецификаций. IEEE 1284 определяет два уровня интерфейсной совместимости. Первый уровень (Level I) определен для устройств медленных, но использующих смену направления передачи данных. Второй уровень (Level II) определен для устройств, работающих в расширенных режимах с высокими скоростями и длинными кабелями. К передатчикам предъявляются следующие требования.

♦ Уровни сигналов без нагрузки не должны выходить за пределы -0,5…+5,5 В.

♦ Уровни сигналов при токе нагрузки 14 мА должны быть не ниже +2,4 В для высокого уровня (V OH) и не выше +0,4 В для низкого уровня (V OL) на постоянном токе.

♦ Выходной импеданс R O, измеренный на разъеме, должен составлять 50±5 Ом на уровне V OH-V OL. Для обеспечения заданного импеданса используют последовательные резисторы в выходных цепях передатчика. Согласование импеданса передатчика и кабеля снижает уровень импульсных помех.

♦ Скорость нарастания (спада) импульса должна находиться в пределах 0,05-0,4 В/нс.

Ниже перечислены требования к приемникам .

♦ Допустимые пиковые значения сигналов -2,0…+7,0 В.

♦ Пороги срабатывания должны быть не выше 2,0 В (V IH) для высокого уровня и не ниже 0,8 В (V IL) для низкого.

♦ Приемник должен иметь гистерезис в пределах 0,2–1,2 В (гистерезисом обладают специальные микросхемы — триггеры Шмитта).

♦ Входной ток микросхемы (втекающий и вытекающий) не должен превышать 20 мкА, входные линии соединяются с шиной питания +5 В резистором 1,2 кОм.

♦ Входная емкость не должна превышать 50 пФ.

Когда появилась спецификация ЕСР, компания Microsoft рекомендовала применение динамических терминаторов на каждую линию интерфейса. Однако в настоящее время следуют спецификации IEEE 1284, в которой динамические терминаторы не применяются. Рекомендованные схемы входных, выходных и двунаправленных цепей приведены на рис. 1.7.

Читать дальшеИнтервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)