Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Канальная адресация ECP применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере. В режиме SPP, если принтер установит сигнал занятости, канал будет занят данными, пока принтер их не примет. В режиме ECP программный драйвер просто адресуется к другому логическому каналу того же порта.

Протокол ECP переопределяет сигналы SPP (табл. 1.6).

Таблица 1.6. Сигналы LPT-порта в режиме ввода-вывода ECP

| Контакт | Сигнал SPP | Имя в ECP | I/O | Описание |

|---|---|---|---|---|

| 1 | Strobe# | HostClk | О | Строб данных, используется в паре с PeriphAck для передачи в прямом направлении (вывод) |

| 14 | AutoLF# | HostAck | О | Указывает тип цикла (команда/данные) при передаче в прямом направлении. Используется как сигнал подтверждения в паре с PeriphClk для передачи в обратном направлении |

| 17 | SelectIn# | 1284Active | O | Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

| 16 | Init# | ReverseRequest# | O | Запрос реверса. Низкий уровень сигнализирует о переключении канала на передачу в обратном направлении |

| 10 | Ack# | PeriphClk | I | Строб данных, используется в паре с HostAck для передачи в обратном направлении |

| 11 | Busy | PeriphAck | I | Используется как сигнал подтверждения в паре с HostClk для передачи в прямом направлении. Индицирует тип команда/данные при передаче в образном направлении |

| 12 | PaperEnd | AckReverse# | I | Подтверждение реверса. Переводится в низкий уровень в ответ на ReverseRequest# |

| 13 | Select | Xflag¹ | I | Флаг расширяемости |

| 15 | Error# | PeriphRequest#¹ | I | Устанавливается ПУ для указания на доступность (наличие) обратного канала передачи¹ |

| 2-9 | Data [0:7] | Data [0:7] | I/O | Двунаправленный канал данных |

¹ Сигналы действуют в последовательности согласования (см. ниже)

Адаптер ECP тоже генерирует внешние протокольные сигналы квитирования аппаратно, но его работа существенно отличается от режима EPP.

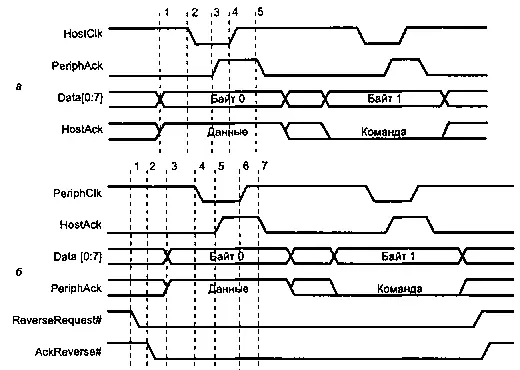

На рис. 1.5, а приведена диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл. Тип цикла задается уровнем на линии HostAck: в цикле данных — высокий, в командном цикле — низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0–6 содержат счетчик RLE (0-127), если единичный — то канальный адрес. На рис. 1.5, б показана пара циклов обратной передачи.

Рис. 1.5. Передача в режиме ECP: а — прямая, б — обратная

В отличие от диаграмм обмена EPP, на рис. 1.5 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO-буфер. Обмен драйвера с FIFO-буфером может осуществляться как с использованием DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ECP. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но обычно важно только то, завершен он или нет.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

1. Хост помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии HostAck.

2. Хост устанавливает низкий уровень на линии HostClk, указывая на действительность данных.

3. ПУ отвечает установкой высокого уровня на линии PeriphAck.

4. Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

5. ПУ устанавливает низкий уровень на линии PeriphAckдля указания на готовность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClkпереходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

Из рис. 1.5 видно и другое отличие ЕСР от EPP. Протокол EPP позволяет драйверу чередовать циклы прямой и обратной передачи, не запрашивая подтверждения на смену направления. В ЕСР смена направления должна быть согласована: хост запрашивает реверс установкой ReverseRequest#, после чего он должен дождаться подтверждения сигналом AckReverse#. Поскольку предыдущий цикл мог выполняться по прямому доступу, драйвер должен дождаться завершения прямого доступа или прервать его, выгрузить буфер FIFO, определив точное значение счетчика переданных байт, и только после этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

1. Хост запрашивает изменение направления канала, устанавливая низкий уровень на линии ReverseRequest#.

2. ПУ разрешает смену направления установкой низкого уровня на линии AckReverse#.

3. ПУ помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии PeriphAck.

4. ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действительность данных.

5. Хост отвечает установкой высокого уровня на линии HostAck.

6. ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может использоваться для фиксации данных хостом.

7. Хост устанавливает низкий уровень на линии HostAckдля указания на готовность к приему следующего байта.

1.3.5. Режимы и регистры ЕСР-порта

Программный интерфейс и регистры ЕСР для адаптеров IEEE 1284 определяет спецификация Microsoft. Порт ЕСР может работать в различных режимах, приведенных в табл. 1.7, где код соответствует полю Modeрегистра ECR(биты [7:5]).

Таблица 1.7. Режимы ЕСР-порта

| Код | Режим |

|---|---|

| 000 | SPP mode , стандартный (традиционный) режим |

| 001 | Bi-directional mode , двунаправленный порт (тип 1 для PS/2) |

| 010 | Fast Centronics , однонаправленный с использованием FIFO и DMA |

| 011 | ЕСР Parallel Port mode , собственно режим ЕСР |

| 100 | ЕРР Parallel Port mode , режим ЕРР¹ |

| 101 | Зарезервировано |

| 110 | Test mode , тестирование работы FIFO и прерываний |

| 111 | Configuration mode , доступ к конфигурационным регистрам |

¹ Этот режим не входит в спецификацию Microsoft, но трактуется как ЕРР многими адаптерами портов, если в CMOS Setup установлен режим ЕСР+ЕРР.

Читать дальшеИнтервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)