Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

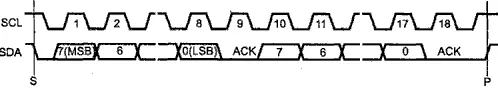

Рис. 11.1. Протокол передачи данных I²C

Начало любой передачи — условие Start — инициируется ведущим устройством, убедившимся в том, что шина свободна (высокий уровень сигналов SCLи SDA). Условие Start (на диаграммах обозначается как S) — перевод сигнала SDAиз высокого в низкий при высоком уровне SCL. Завершается операция переводом сигнала SDAиз низкого уровня в высокий при высоком уровне SCL — условие Stop (обозначается как P), также вводящееся ведущим устройством. При передаче данных состояние линии SDAможет изменяться только при низком уровне SCL, биты данных считаются действительными во время высокого уровня SCL Ведущее устройство может начать очередную передачу вслед за текущей, не вводя условие Stop , — это называется repeated Start (повторный старт, обозначающийся Sr). В протоколе условия Sи Srпочти равнозначны. Каждая посылка данных состоит из 8 бит данных, формируемых передатчиком (старший бит — MSB — передается первым), после чего передатчик на один такт освобождает линию данных для получения подтверждения. Приемник во время девятого такта формирует бит подтверждения Ack, по которому передатчик убеждается, что его «услышали». После передачи бита подтверждения ведомое устройство может задержать следующую посылку, удерживая линию SCLна низком уровне. Ведомое устройство в режимах F/S может замедлить передачу по шине и на уровне приема каждого бита, удерживая SCLна низком уровне после его спада, сформированного передатчиком. Поэтому ведущее устройство должно генерировать сигнал SCLне «вслепую», а анализируя состояние линии SCL: сняв этот сигнал, новый импульс (открытие ключа передатчика) оно имеет право вводить, лишь убедившись, что сигнал SCLвернулся в пассивное состояние (высокий уровень). В противном случае синхронизация будет потеряна. Сигнал SCLможет быть растянут и другим устройством, пытающимся захватить шину в это же время. Тактовый сигнал SCLне обязательно будет равномерным: время его нахождения на низком уровне будет определяться максимальным временем, в котором его захочет удержать самое медленное из устройств, участвующих в данном обмене (даже и конфликтующих); время нахождение на высоком уровне будет определяться самым быстрым из конфликтующих ведущих устройств.

Коллизия (конфликт) на шине может возникнуть, когда два (или более) устройства, убедившись в покое шины, одновременно (или почти одновременно) инициируют обмен данными. Все они управляют линиями SCLи SDAи наблюдают за ними. Если устройство, передающее единицу (высокий уровень), в данном такте на линии SDAвидит ноль (низкий уровень), оно должно признать свой проигрыш в конфликте и освободить линии SCLи SDA(при этом ему позволительно управлять линией SCLдо конца передачи текущего байта). Выигравшее устройство даже и не заметит проигравших конкурентов и продолжит работу. Арбитраж может закончиться в любом месте посылки, формируемой ведущим устройством. Искажения информации, передаваемой выигравшим устройством, не происходит (приятное отличие от коллизий в сетях Ethernet). Если ведущее устройство, проигравшее в конфликте, имеет и функции ведомого устройства, по признанию проигрыша оно должно перейти в режим ведомого, поскольку конфликт мог быть вызван и попыткой обращения к нему победившего ведущего устройства.

Бит подтверждения ACK, вводящийся в конце каждого байта устройством- приемником, выполняет несколько функций. Когда передатчиком является ведущее устройство , приемник (ведомый) должен вводить нулевой бит ACK, свидетельствующий о нормальном получении очередного байта. Единичный бит ACK(нет подтверждения) в ответ на посылку адреса свидетельствует об отсутствии адресованного ведомого устройства на шине или его занятости внутренними процессами. Отсутствие подтверждения байта данных свидетельствует о занятости устройства. Не получив бита подтверждения, ведущее устройство должно сформировать условие Stop , чтобы освободить шину. Когда ведущее устройство является приемником , оно должно формировать нулевой бит ACKпосле каждого принятого байта, кроме последнего. Единичный бит ACKв этом случае является указанием ведомому устройству на окончание передачи — оно теперь должно освободить линии SDAи SCL, чтобы ведущее устройство смогло сформировать условие Pили Sr.

На вышеописанной физической основе строится протокол обмена данными по I²C. Каждое ведомое устройство имеет свой адрес, уникальный на шине. В начале любой передачи ведущее устройство после условия Sили Srпосылает адрес ведомого устройства или специальный адрес (табл. 11.1). Ведомое устройство, опознавшее свой адрес после условия Start , становится выбранным ; оно обязано ответить подтверждением на адрес и последующие сигналы со стороны ведущего устройства, до получения условия Pили Sr. В первоначальном варианте интерфейса разрядность адреса устройства составляла 7 бит, впоследствии был введен и режим 10-битной адресации, совместимый с 7-битной. На одной шине могут присутствовать устройства и с 7-битной, и 10-битной адресацией.

Таблица 11.1. Специальные адреса I²C

| Биты[7:1] | Бит 0 (RW) | Назначение |

|---|---|---|

| 0000000 | 0 | General call address — адрес общего вызова |

| 0000 000 | 1 | Start — начало активного обмена |

| 0000 001 | X | Адрес устройства шины CBUS (для совместимости) |

| 0000 010 | X | Адрес для устройств иных шин |

| 0000 011 | X | Зарезервировано |

| 0000 1XX | X | Код ведущего устройства режима Hs |

| 1111 1XX | X | Зарезервировано |

| 1111 0XX | X | Признак 10-битной адресации |

При 7-битной адресации в первом байте после S( Sr) ведущее устройство передает 7 бит адреса (А[6:0] в битах [7:1]) и признак операции RW(в бите 0 RW=1 — чтение, RW=0 — запись). Адреса ведомых устройств не должны попадать в области, указанные в таблице. Диапазоны адресов устройств различных типов централизованно выдаются изготовителям микросхем фирмой Philips. Для микросхем памяти, например, 7-битный адрес содержит две части: старшие 4 бита А[6:3] несут информацию о типе устройства (EEPROM — 1010), а младшие 3 бита А[0:2] определяют номер устройства данного типа на шине. Микросхемы с интерфейсом I²C имеют три адресных входа, коммутацией которых на логические уровни 1 и 0 задается номер устройства, на который оно «отзовется», а тип устройства «зашит» в нем самом его изготовителем.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)