Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

² Поддержка автоматического конфигурирования. Для ISA PnP является позднейшей надстройкой, реализуемой адаптерами и ПО.

6.1. Шины ISA, EISA и PC/104

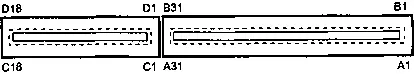

ISA Bus (Industry Standard Architecture) — шина расширения, применявшаяся с первых моделей PC и ставшая промышленным стандартом, В компьютере XT использовалась шина с разрядностью данных 8 бит и адреса — 20 бит. В компьютерах AT ее расширили до 16 бит данных и 24 бит адреса. Конструктивно, как показано на рис. 6.1, шина выполнена в виде двух щелевых разъемов с шагом выводов 2,54 мм (0,1 дюйма). В подмножестве ISA-8 используется только 62-контактный слот (ряды А, В), в ISA-16 применяется дополнительный 36-контактный слот (ряды С, D). Шина PC/104, разработанная для встраиваемых контроллеров на базе PC, отличается от обычной ISA только конструктивно. В шине EISA — дорогом 32-разрядном расширении ISA — используется «двухэтажный» слот, позволяющий устанавливать и обычные карты ISA.

Рис. 6.1. Слот ISA

Для шины ISA выпущено (и продолжает выпускаться) огромное количество разнообразных карт расширения. Ряд фирм выпускает карты-прототипы (Prototype Card), представляющие собой печатные платы полного или уменьшенного формата с крепежной скобой. На платах установлены обязательные интерфейсные цепи — буфер данных, дешифратор адреса и некоторые другие. Остальная часть платы свободна, и здесь разработчик может разместить макетный вариант своего устройства. Эти платы удобны для проверки нового изделия, а также для монтажа единичных экземпляров устройства, когда разработка и изготовление печатной платы нерентабельно.

В каждый момент времени шиной может управлять только одно устройство- задатчик , обращающееся к ресурсам (портам или ячейкам памяти) устройств-исполнителей. Шина ISA обеспечивает возможность обращения к 8- или 16-битным регистрам устройств, отображенным на пространства ввода-вывода и памяти. Диапазон адресов памяти для устройств ограничен областью верхней памяти UMА (А0000-FFFFFh). Для шины ISA-16 настройками CMOS Setup может быть разрешено пространство между 15-м и 16-м мегабайтом памяти (при этом компьютер не сможет использовать более 15 Мбайт ОЗУ). Для шины ISA диапазон адресов ввода-вывода сверху ограничен количеством задействованных для дешифрации бит адреса, нижняя областью адресов 0-FFh недоступна (зарезервирована под устройства системной платы). В PC была принята 10-битная адресация ввода-вывода, при которой линии адреса А[15:10]устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100h–3FFh. Впоследствии стали применять 12-битную адресацию (диапазон 100h-FFFh). При этом приходится учитывать возможность присутствия на шине старых 10-битных адаптеров, которые «отзовутся» на адрес с подходящими ему битами А[9:0]во всей допустимой области 12-битного адреса четыре раза (у каждого 10-битного адреса будет еще по три 12-битных псевдонима). Полный 16-битный адрес используется только в шинах EISA и PCI.

Шина ISA-8 может предоставить до 6 линий запросов прерываний, ISА-16 — 11. Часть из них могут «отобрать» устройства системной платы или шина PCI.

Шина ISA-8 позволяет использовать до трех 8-битных каналов DMA. На 16-битной шине доступны еще три 16-битных и один 8-битный канал.

Все перечисленные ресурсы шины должны быть бесконфликтно распределены. Бесконфликтность подразумевает выполнение перечисленных ниже условий.

♦ Каждое устройство-исполнитель должно управлять шиной данных только при чтении по его адресам или по используемому им каналу DMA. Области адресов, по которым выполняется чтение регистров различных устройств, не должны пересекаться. Поскольку при записи шиной данных управляет лишь текущий задатчик, возможность конфликтов, приводящих к искажениям данных, исключена. «Подсматривать» операции записи, адресованные не данному устройству, не возбраняется.

♦ Назначенную линию IRQxили DRQxустройство должно держать на низком уровне в пассивном состоянии и переводить в высокий уровень для активации запроса. Неиспользуемыми линиями запросов устройство управлять не имеет права, они должны электрически отсоединяться или подключаться к буферу, находящемуся в третьем состоянии. Одной линией запроса может пользоваться только одно устройство. Такая нелепость (с точки зрения схемотехники ТТЛ) была допущена в первых PC и из требований совместимости тиражируется до сих пор.

Задача распределения ресурсов для старых адаптеров решалась с помощью джамперов, затем появились программно конфигурируемые устройства, которые вытесняются автоматически конфигурируемыми платами PnP.

Назначение контактов слотов шин ISA и EISA приведено в табл. 6.2 и 6.3.

Таблица 6.2. Основной разъем шин ISA-8, ISA-16 и EISA

| Ряд В | № | Ряд А |

|---|---|---|

| GND | 1 | IOCHK# |

| Reset | 2 | SD7 |

| +5 В | 3 | SD6 |

| IRQ2/9¹ | 4 | SD5 |

| -5 В | 5 | SD4 |

| DRQ2 | 6 | SD3 |

| -12 В | 7 | SD2 |

| 0WS#² | 8 | SD1 |

| +12 В | 9 | SD0 |

| GND | 10 | IOCHRDY |

| SMEMW# | 11 | AEN |

| SMEMR# | 12 | SA19 |

| IOWR# | 13 | SA18 |

| IORD# | 14 | SA17 |

| DACK3# | 15 | SA16 |

| DRQ3 | 16 | SA15 |

| DACK1# | 17 | SA14 |

| DRQ1 | 18 | SA13 |

| REFRESH# | 19 | SA12 |

| BCLK | 20 | SA11 |

| IRQ7 | 21 | SA10 |

| IRQ6 | 22 | SA9 |

| IRQ5 | 23 | SA8 |

| IRQ4 | 24 | SA7 |

| IRQ3 | 25 | SA6 |

| DACK2# | 26 | SA5 |

| TC | 27 | SA4 |

| BALE | 28 | SA3 |

| +5 В | 29 | SA2 |

| Osc | 30 | SA1 |

| GND | 31 | SA0 |

¹ B4: XT=IRQ2, AT=IRQ9.

² B8: XT-Card Selected.

Таблица 6.3. Дополнительный разъем шин ISA-16 и EISA

| Ряд D | № | Ряд С |

|---|---|---|

| MEMCS16# | 1 | SBHE# |

| IOCS16# | 2 | LA23 |

| IRQ10 | 3 | LA22 |

| IRQ 11 | 4 | LA21 |

| IRQ12 | 5 | LA20 |

| IRQ 15 | 6 | LA19 |

| IRQ14 | 7 | LA18 |

| DACK0# | 8 | LA17 |

| DRQ0 | 9 | MEMR# |

| DACK5# | 10 | MEMW# |

| DRQ5 | 11 | SD8 |

| DACK6# | 12 | SD9 |

| DRQ6 | 13 | SD10 |

| DACK7# | 14 | SD11 |

| DRQ7 | 15 | SD12 |

| +5 B | 16 | SD13 |

| MASTER# | 17 | SD14 |

| GND | 18 | SD15 |

Сигналы шины ISA естественны для периферийных микросхем фирмы Intel (в стиле семейства 8080). Набор сигналов ISA-8 предельно прост. Программное обращение к ячейкам памяти и пространства ввода-вывода обеспечивают следующие сигналы.

♦ SD[7:0]— шина данных. Иное название сигналов — Dataили D.

♦ SA[19:0]( Addr[19:0], A[19:0]) — шина адреса.

♦ AEN— разрешение адресации портов (запрещает ложную дешифрацию адреса в цикле DMA).

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)