Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

♦ IOW#( IOWC#, IOWR#) — запись в порт.

♦ IOR#( IORC#, IORD#) — чтение порта.

♦ SMEMW#( SMEMWR#, SMWTC#) — запись в системную память (в диапазоне адресов 0-FFFFFh).

♦ SMEMR#( SMEMRD#, SMRDC#) — чтение системной памяти (в диапазоне адресов 0-FFFFFh).

Ниже перечислены сигналы, относящиеся к сигналам запросов прерывания и каналам прямого доступа к памяти.

♦ IRQ2/9, IRQ[3:7]— запросы прерываний. Положительный перепад сигнала вызывает запрос аппаратного прерывания. Для идентификации источника высокий уровень должен сохраняться до подтверждения прерывания процессором, что затрудняет разделение (совместное использование) прерываний. Линия IRQ2/9 в шинах XT вызывает аппаратное прерывание с номером 2, а в AT — с номером 9.

♦ DRQ[1:3]— запросы 8-битных каналов DMA (положительным перепадом).

♦ DACK[1:3]#— подтверждение запросов 8-битных каналов DMA.

♦ TC— признак завершения счетчика циклов DMA.

Шина имеет и несколько служебных сигналов синхронизации, сброса и регенерации памяти, установленной на адаптерах.

♦ IOCHRDY( CHRDY, I/OCHRDY) — готовность устройства, низкий уровень удлиняет текущий цикл (не более 15 икс).

♦ BALE( ALE) — разрешение защелки адреса. После его спада в каждом цикле процессора линии SA[0:19]гарантированно содержат действительный адрес.

♦ REFRESH#( REF#) — цикл регенерации памяти (в XT называется DACK0#). Сигнал появляется каждые 15 мкс, при этом шина адреса указывает на очередную регенерируемую строку памяти.

♦ IOCHK#— контроль канала, низкий уровень вызывает NMI CPU (разрешение и индикация в системных портах 061h, 062h).

♦ RESET( RESDRV, RESETDRV) — сигнал аппаратного сброса (активный уровень — высокий).

♦ BCLK( CLK) — синхронизация шины с частотой около 8 МГц. ПУ могут не использовать этот сигнал, работая только по управляющим сигналам записи и чтения.

♦ OSC— несинхронизированная с шиной частота 14,431818 МГц (использовалась старыми дисплейными адаптерами).

Кроме логических сигналов шина имеет контакты для разводки питания +5, -5, +12 и -12 В.

Дополнительный разъем , расширяющий шину до 16-битной, содержит линии данных, адреса, запросов прерываний и каналов прямого доступа.

♦ SD[15:8]— шина данных.

♦ SBHE#— признак наличия данных на линиях SD[15:8].

♦ LA[23:17]— нефиксированные сигналы адреса, требующие защелкивания по спаду сигнала BALE. Такой способ подачи адреса позволяет сократить задержку. Кроме того, схемы дешифратора адреса памяти плат расширения начинают декодирование несколько раньше спада BALE.

♦ IRQ[10:12], IRQ[14:15]— дополнительные запросы прерываний.

♦ DRQ[5:7]— запросы 16-битных каналов DMA (положительным перепадом).

♦ DACK[5:7]#— подтверждение запросов 16-битных каналов DMA.

♦ DRQ0и DACK0#— запрос и подтверждение 8-битного канала DMA, освободившегося от регенерации памяти.

Перечисленные ниже сигналы связаны с переключением разрядности данных.

♦ МEMCS16#( M16#) — адресуемое устройство поддерживает 16-битные обращения к памяти.

♦ IOCS16#( I/OCS16#, IO16#) — адресуемое устройство поддерживает 16-битные обращения к портам.

К новым управляющим сигналам относятся следующие.

♦ MEMW#( MWTC#) — запись в память в любой области до 16 Мбайт.

♦ MEMR#( MRDC#) — чтение памяти в любой области до 16 Мбайт.

♦ OWS#( SRDY#, NOWS#, ENDXFR) — укорочение текущего цикла по инициативе адресованного устройства.

♦ MASTER#( MASTER16#) — запрос от устройства, использующего 16-битный канал DMA на управление шиной. При получении подтверждения DACK[5:7]Bus-Master может захватить шину.

В шине EISA на дополнительных контактах слотов (недоступных картам ISA) располагается расширение шин данных и адреса до 32 бит, а также набор сигналов, обеспечивающих передачу данных в синхронном режиме с возможностью пакетных циклов.

6.1.1. Обычная передача данных

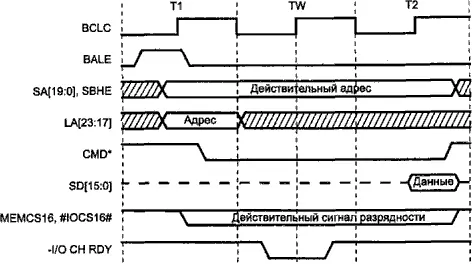

Для передачи данных от исполнителя к задатчику предназначены циклы чтения ячейки памяти или порта ввода-вывода, для передачи данных от задатчика к исполнителю — циклы записи ячейки памяти или порта ввода-вывода. В каждом цикле текущий (на время данного цикла) задатчик формирует адрес обращения и управляющие сигналы, а в циклах записи еще и данные на шине. Адресуемое устройство-исполнитель в соответствии с полученными управляющими сигналами принимает (в цикле записи) или формирует (в цикле чтения) данные. Также оно может, при необходимости, управлять длительностью цикла и разрядностью передачи. Обобщенные временные диаграммы циклов чтения или записи памяти или ввода-вывода приведены на рис. 6.2. Здесь условный сигнал CMD* изображает один из следующих сигналов:

♦ SMEMR#, MEMR#— в цикле чтения памяти;

♦ SMEMW#, MEMW#— в цикле записи памяти;

♦ IOR#— в цикле чтения порта ввода-вывода;

♦ IOW#— в цикле записи порта ввода-вывода.

Рис. 6.2. Временные диаграммы циклов чтения или записи на шине ISA

В каждом из рассматриваемых циклов активными (с низким уровнем) могут быть только сигналы лишь из одной строки данного списка, и во время всего цикла сигнал AENимеет низкий уровень. Цикл прямого доступа к памяти, в котором это правило не соблюдается, рассмотрен ниже, и в таком цикле сигнал AENбудет иметь высокий уровень. Сигналы SMEMR#и SMEMW#вырабатываются из сигналов MEMR#и MEMW#соответственно, когда адрес принадлежит диапазону 0-FFFFFh. Поэтому сигналы SMEMR#и SMEMW#задержаны относительно MEMR#и MEMW#на 5-10 нс.

В начале каждого цикла контроллер шины устанавливает адрес обращения: на линиях SA[19:0]и SBHE#действительный адрес сохраняется на время всего текущего цикла; на линиях LA[23:17]адрес действителен только в начале цикла, так что требуется его «защелкивание». Каждое устройство имеет дешифратор адреса — комбинационную схему, срабатывающую только тогда, когда на шине присутствует адрес, относящийся к данному устройству. В фазе адресации устройства еще «не знают», к какому из пространств (памяти или ввода-вывода) относится выставленный адрес. Но дешифраторы адресов уже срабатывают, и, когда в следующей фазе шина управления сообщает тип операции, адресуемое устройство уже оказывается готовым к ее исполнению. Если устройство использует линии LA[23:17](они нужны лишь для обращений к памяти выше границы FFFFFh), то они на дешифратор адреса должны проходить через регистр-защелку, «прозрачный» во время действия сигнала BALEи фиксирующий состояние выходов по его спаду. Это позволяет дешифратору, всегда вносящему некоторую задержку, начинать работу раньше, чем поступит управляющий сигнал чтения или записи. При обращении к портам ввода-вывода сигналы LA[32:17]не используются.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)