Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

3. Контроллер модифицирует счетчик адреса и повторяет шаги 1–2 для каждого следующего сигнала DRQx, пока не будет исчерпан счетчик циклов. В последнем цикле обмена контроллер формирует общий сигнал окончания TC(Terminate Count), который может быть использован устройством для формирования сигнала аппаратного прерывания.

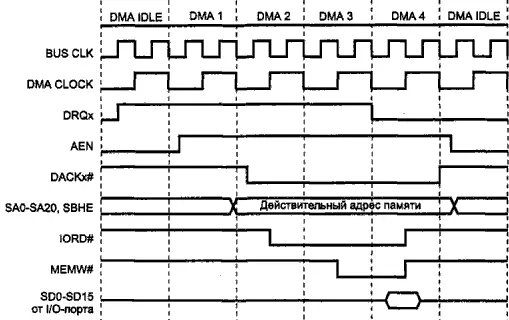

Рис. 6.3. Цикл обмена DMA

Диаграмма обратной пересылки (из памяти в ПУ) отличается только тем, что на месте сигнала IOR#будет сигнал MEMR#, а на месте MEMW#— сигнал IOW#. Направление обмена и параметры режима задаются программированием контроллера DMA.

Цикл DMA, и так довольно длинный, может быть растянут устройством с помощью сигнала IOCHRDY(но сократить его сигналом 0WS#невозможно). Запрашивать удлинение цикла может только адресованная память — подразумевается, что когда ПУ выставляет запрос DRQx, оно уже должно быть готово к обмену.

На 16-битной шине ISA доступно 7 каналов DMA: четыре 8-битных (номера 0–3) и три 16-битных (5–7), подключенные к первичному и вторичному контроллерам соответственно. Канал 4 используется для каскадирования (соединения контроллеров). На 8-битном слоте доступны только четыре 8-битных канала (в XT только 3 — канал 0 требовался для регенерации памяти).

Кроме приведенного на рисунке режима одиночной передачи возможны и иные, описанные в п. 12.4.

Напомним, что по 8-битным каналам DMA за один сеанс настройки контроллера можно передавать не более 64К байт данных, начинающихся с любого адреса (но не пересекая границ страниц, см. п. 12.3.2 и 12.5). По 16-битным каналам за сеанс можно передавать не более 64К слов данных, начинающихся с четного адреса, и границы страниц иные. Используя DMA в режимах, отличных от одиночного, длительность непрерывной передачи не должна превышать 15 мкс (для обеспечения регенерации памяти).

6.1.3. Прямое управление шиной

В случае прямого управления шиной (bus mastering) инициатором обмена становится контроллер какого-либо устройства или интерфейса, но не процессор и не канал DMA. Прямое управление позволяет контроллеру, не отвлекая центральный процессор, выполнять обмен данными с высокой производительностью и, возможно, по более сложным правилам и без ограничений, присущих каналам DMA (невозможность пересечения границы страницы). Контроллер, как правило, обеспечивает обмен данными между системным ОЗУ и своим периферийным устройством или интерфейсом. В принципе он может общаться с памятью или портами другого абонента шины, но для упрощения организации всех информационных связей центральным «перевалочным пунктом» все-таки является системное ОЗУ. Получить право на управление шиной ISA может только контроллер, подключенный к 16- битному слоту. Для арбитража запросов на управление шиной от нескольких источников — центрального процессора, контроллера DMA и контроллеров- абонентов шины используется второй контроллер DMA (каналы 5–7). Устройство, желающее получить управление, выставляет запрос DRQx(x=5…7), по которому контроллер DMA запрашивает управление шиной у центрального процессора. Получив подтверждение от процессора, контроллер устанавливает сигнал AEN(для блокировки дешифрации адреса портов) и формирует сигнал DACKx. Получив этот сигнал, устройство устанавливает низкий уровень на линии MASTER#, по которому контроллер шины DMA снимает сигнал AENи освобождает линии командных сигналов. Таким образом, управление шиной переходит к данному устройству до тех пор, пока оно не снимет запрос DRQx. В режиме прямого управления шиной ISA устройство становится полновластным и бесконтрольным хозяином как самой шины, так и системы в целом (через мост шины). Если шина захватывается более чем на 15 мкс, контроллер устройства должен заботиться о регенерации памяти (см. ниже). Устройства (и память), к которым обращается задатчик шины, могут потребовать введения тактов ожидания сигналом IOCHRDY, и это требование должно удовлетворяться.

6.1.4. Регенерация памяти

Динамическая память, применяемая в компьютере в качестве системного ОЗУ, а также, возможно, находящаяся на картах расширения, требует регенерации — периодического обновления (refresh) всех строк матрицы. На системной плате всегда имеется контроллер регенерации памяти, в задачу которого входит регулярный перебор строк памяти с формированием специального цикла регенерации. Каждые 15 мкс контроллер регенерации формирует цикл регенерации (сигнал REFRESH#), диаграмма которого аналогична циклу DMA, но вместо чтения данных выполняется регенерация. В этом цикле считывания данных из микросхем памяти не производится, но стробы строк формируются (подробнее о методах регенерации см. в книге «Аппаратные средства IBM PC. Энциклопедия»). На шине ISA контроллер регенерации работает как нулевой канал DMA (в старых машинах он непосредственно и использовался). Каждые 15 мкс контроллер регенерации формирует сигнал REFRESH#, во время действия которого устанавливается AEN=H и BALE=H, формируется сигнал MEMR#, а на линиях SA[7:0]устанавливается адрес текущей регенерируемой строки. Диаграмма цикла регенерации аналогична циклу DMA, но сигнал REFRESH#указывает на то, что вместо чтения данных выполняется регенерация.

Если какое-либо устройство захватывает управление шиной более чем на 15 мкс, оно должно позаботиться о регенерации памяти. Для этого раз в 15 мкс оно должно вырабатывать сигнал REFRESH#, «отпуская» все адресные и управляющие сигналы. При этом контроллер шины, расположенный на системной плате и отвечающий за регенерацию памяти, сформирует очередной адрес на линиях SA[7:0]и сигнал MEMR#, а также установит AEN=0 и BALE=1 на все время цикла регенерации. Если устройство, надолго захватившее шину, сигнал регенерации не формирует, то запросы регенерации накапливаются в контроллере регенерации, и, как только управление будет возвращено, эти запросы будут немедленно удовлетворены. Однако число безнаказанно пропущенных запросов ограничено свойствами динамической памяти, и очередь запросов в контроллере регенерации может ограничиваться, например, четырьмя.

6.1.5. Прерывания

На шине ISA имеются линии запросов маскируемых и немаскируемых аппаратных прерываний. Линии запросов маскируемых прерываний IRQ2- IRQ7поступают на входы первичного контроллера прерываний, IRQ9- IRQ15— на входы вторичного. Контакт B4 ( IRQ2/9) запрос IRQ2вырабатывал только у машин PX/XT. На всех современных машинах (класса AT) он является запросом IRQ9, хотя на многих адаптерах (всех 8-битных) он обозначается как IRQ2. Приоритеты у запросов убывают по порядку IRQ9… IRQ15и далее IRQ3… IRQ7. Запросы от конкретных линий могут быть замаскированы записью в регистры контроллера (см. п. 12.4), общий запрет/разрешение осуществляется манипулированием флагом разрешения прерываний ( IF) процессора. Устройство может использовать одну или несколько линий запроса прерывания. На используемой линии запроса устройство в покое должно формировать низкий уровень сигнала, а при возникновении условия прерывания устанавливать на нем высокий уровень запроса. Неиспользуемые линии должны быть электрически отключены от шины или же их выходные формирователи должны переводиться в третье состояние. Переход из низкого в высокий уровень является сигналом для контроллера прерываний на формирование запроса прерывания к процессору. Устройство должно удерживать высокий уровень запроса до тех пор, пока к нему не обратится программа-обработчик прерывания, что будет означать не только обнаружение, но и правильную идентификацию источника запроса прерывания. Если запрос снят преждевременно, идентификация будет некорректной. Детально механизм обслуживания прерываний рассмотрен в п. 12.4.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)