Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей

- Название:OrCAD PSpice. Анализ электрических цепей

- Автор:

- Жанр:

- Издательство:ДМК Пресс, Питер

- Год:2008

- Город:Москва, Санкт-Петербург

- ISBN:978-5-9706-0009-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей краткое содержание

Это руководство по работе в программе OrCAD Pspice предназначено для всех, кто знаком с основными разделами электротехники. При постепенном усложнении задач объясняются все необходимые аспекты работы в OrCAD Pspice, что позволяет творчески применять их при дальнейшем анализе электрических и электронных схем и устройств. Рассмотрение материала начинается с анализа цепей постоянного тока, продолжается анализом цепей переменного тока, затем переходит к различным разделам полупроводниковой электроники. Информация изложена таким образом, чтобы каждый, кто изучал или изучает определенный раздел электротехники, мог сразу же использовать OrCAD Pspice на практике. Больше внимания, чем в других книгах по этой теме, уделяется созданию собственных моделей и использованию встроенных моделей схем в OrCAD Pspice.

На прилагаемом к книге DVD вы найдете демонстрационную версию программы OrCAD PSpice Student Edition 9, которой можно пользоваться свободно. Кроме того, на диске размещена версия OrCAD 10.5 Demo Release, с которой можно работать в течение 30 дней после установки на компьютер.

OrCAD PSpice. Анализ электрических цепей - читать онлайн бесплатно ознакомительный отрывок

Интервал:

Закладка:

.OP

.TF V([4]) V_Vs

.PROBE

*Netlist File:

.INC "hparmod-SCHEMATIС1.net"

*Alias File:

**** INCLUDING hparmod-SCHEMATIC1.net ****

* source HPARMOD

F_F 4 0 VF_F 50

VF_F 3 5 0V

E_E 5 0 4 0 2.5E-4

R_RL 4 0 10k

R_Ro 4 0 40k

R_Ri 2 3 1.1k

R_Rs 1 2 1k

V_Vs 1 0 1mV

**** RESUMING hparmod-SCHEMATIC1-hpamods.sim.cir

**** .INC "hparmod-SCHEMATIC1.als"

INCLUDING hparmod-SCHEMATIC1.als ****

.ALIASES

F_F F(3=4 4=0 )

VF_F F(1=3 2=5 )

E_E E(3=5 4=0 1=4 2=0 )

R_RL RL(1=4 2=0 )

R_Ro Ro(1=4 2=0 )

R_Ri Ri(1=2 2=3 )

R_Rs Rs(1=1 2=2 )

V_Vs Vs(+=l -=0 )

_ _(1=1)

_ _(2=2)

_ _(3=3)

_ _(4=4)

_ _(5=5)

.ENDALIASES

**** RESUMING hparmod-SCHEMATIC1-hparmods.sim.cir ****

.END

**** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) .0010 ( 2) 500.0Е-06 ( 3) -50.00E-06 ( 4) -.2000

( 5) -50.00E-06

VOLTAGE SOURCE CURRENTS

NAME CURRENT

VF_F 5.000E-07

V_Vs -5.000E-07

TOTAL POWER DISSIPATION 5.00E-10 WATTS

**** VOLTAGE-CONTROLLED VOLTAGE SOURCES

NAME E_E

V-SOURCE -5.000E-05

I-SOURCE 5.000E-07

**** CURRENT-CONTROLLED CURRENT SOURCES

NAME F_F

I-SOURCE 2.500E-05

**** SMALL-SIGNAL CHARACTERISTICS

V(4)/V_Vs = -2.000E+02

INPUT RESISTANCE AT V_Vs = 2.000E+03

OUTPUT RESISTANCE AT V(4) = 8.400E+03

Рис. 15.21. Выходной файл для модели в h -параметрах

Упражнение по созданию графической схемы было, однако, поучительно, и анализ заслуживает внимания, по крайней мере, с этой точки зрения. Обратите внимание на строку файла псевдонимов для зависимого источника E_E:

E_E 5 0 4 0 2.5Е- 4

Первые два полюса (5, 0) — выходные полюсы, показывают расположение зависимого источника в схеме, в то время как входные полюсы (4, 0) указывают на управляющее напряжение (от которого зависит E) снимаемое с R 0. Зависимый источник F_F описан как

F_F 4 0 VF_F 50

Первые два полюса (4, 0) являются выходными полюсами, показывающими, где вводится в схему ток F. Входные полюсы включены в контур последовательно с компонентами, через которые проходит независимый ток (управляющий источником F ). В команде F_F эта управляющая цепь показана именем источника напряжения в контуре. Контур, через который проходит ток I b , включает также и напряжение Е, что ясно видно из схемы.

В перечне элементов (netlist) имеется команда ввода

VF_F 3 5 0V

Эта строка была сформирована программой, чтобы ввести в листинг источник И), который был необходим в схеме на рис. 3.7 вместе с листингом F, который использовался в PSpice.

Не забудьте, что наши результаты можно при желании представить в действующих значениях для переменных составляющих, и обратите внимание на следующее: ток через источник напряжения VF_F равен 5.000Е-07 А. Это ток базы. С помощью других известных значений это легко проверить:

Источники напряжения, управляемые напряжением, обозначенные на рис. 15.21 как V-SOURCE , задают напряжение на узле 3, равное -50 мкВ, а компонент I-SOURCE создает ток в выходном контуре F. Поскольку коэффициент усиления источника F равен 50, ток F= 50 I b =25 мА. После деления между двумя сопротивлениями ток через RL равен (0,8·25)мкА=20 мкА. На рисунке этот ток направлен вверх, что нужно показать также и на вашей схеме. Напряжение на узле 4 равно (-20 мкА)(10 кОм)=0,2 В, что подтверждает значение, приведенное в выходном файле. Это отрицательное выходное напряжение, инвертированное относительно напряжения V s .

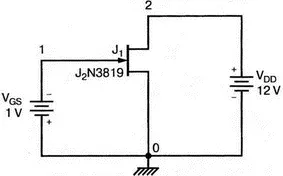

Характеристики полевых транзисторов

Демонстрационная версия OrCAD имеет компоненты J2N3819 и J2N4393 в качестве моделей для полевых n-канальных транзисторов (JFET). Чтобы получить семейство выходных характеристик, создайте новый проект с именем Jfetch. Используем простую схему (рис. 15.22). Номинальные значения для V GS и V DD показаны на рисунке. Определите опции моделирования в Simulation Profile, используя имя jfetchs. Внутренний цикл вариации использует значения источника напряжения V DD от 0 до 12 В с шагом в 0,2 В. Внешний цикл определяется изменением напряжения V GS от 0 до 4 В с шагом в 1 В.

Рис. 15.22. Схема смещения для n-канального полевого транзистора

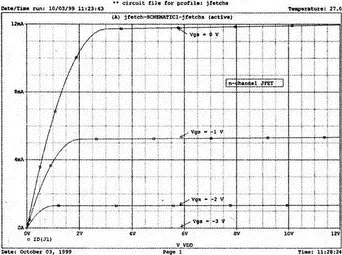

Выполните моделирование и получите в Probe график ID(J1). Вы должны получить семейство кривых с параметром VGS, приведенных на рис. 15.23. Кривые показывают, что наибольшие токи соответствуют V GS =0. Ниже расположена кривая с параметром V GS =–1 В и так далее. Напряжением отсечки является V GS=– 3 В.

Рис. 15.23. Ток стока в n -канальном полевом транзисторе

Выходной файл включает параметры модели J2N3S19 : пороговое напряжение (отсечки) VTO=- 3 В, коэффициент передачи BETA и другие. Они отражены на рис. 15.24. В приложении D приведены все параметры модели для J (JFET).

**** 10/03/99 11:45:33 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: jfetchs

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.DC LIN V VDD 0V 12V 0.2V

+ LIN V_VGS 0V 4V 1V

.PROBE

*Netlist File:

.INC "jfetch-SCHEMATIC1.net"

*Alias File:

**** INCLUDING jfetch-SCHEMATIC1.net ****

* source JFETCH

J_J1 2 1 0 J2N3819

V_VDD 2 0 12V

V_VGS 0 1 1V

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir

**** .INC "jfetch-SCHEMATIC1.als"

**** INCLUDING jfetch-SCHEMATIC1.als ****

.ALIASES

J_J1 J1(d=2 g=1 s=0 )

V_VDD VDD(+=2 -=0 )

V_VGS VGS(+=0 -=1 )

_ _(1=1)

_ _(2=2)

.ENDALIASES

.END

**** Junction FET MODEL PARAMETERS

J2N3819

NJF

VTO -3

BETA 1.304000E-03

LAMBDA 2.250000E-03

IS 33.570000E-15

ISR 322.400000E-15

ALPHA 311.700000E-06

VK 243.6

RD 1

RS 1

CGD 1.600000E-12

CGS 2.414000E-12

M .3622

VTOTC -2.500000E-03

BETATCE -.5

KF 9.882000E-18

Рис. 15.24. Выходной файл для n -канального полевого транзистора

Хотя предыдущие выпуски программного обеспечения от MicroSim использовали для создания рисунков программу Schematics вместо Capture, автоматически формируя команду .ОР в схемном файле, используемая в книге версия Capture этого не делает. Следовательно, значения параметров смещения не выводятся в выходном файле. Чтобы получить эти значения, отредактируете параметры настройки моделирования и запросите анализ параметров смещения путем проверки с опцией .OP. Выходной файл при таком запуске показан на рис. 15.25. Информация, дублирующая информацию предыдущего выходного файла, из него удалена. Убедитесь, что выходной файл соответствует графику, показывая V DD= 12 В, V GS =–1 В, I DD =5,328 мА.

Читать дальшеИнтервал:

Закладка: