Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей

- Название:OrCAD PSpice. Анализ электрических цепей

- Автор:

- Жанр:

- Издательство:ДМК Пресс, Питер

- Год:2008

- Город:Москва, Санкт-Петербург

- ISBN:978-5-9706-0009-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей краткое содержание

Это руководство по работе в программе OrCAD Pspice предназначено для всех, кто знаком с основными разделами электротехники. При постепенном усложнении задач объясняются все необходимые аспекты работы в OrCAD Pspice, что позволяет творчески применять их при дальнейшем анализе электрических и электронных схем и устройств. Рассмотрение материала начинается с анализа цепей постоянного тока, продолжается анализом цепей переменного тока, затем переходит к различным разделам полупроводниковой электроники. Информация изложена таким образом, чтобы каждый, кто изучал или изучает определенный раздел электротехники, мог сразу же использовать OrCAD Pspice на практике. Больше внимания, чем в других книгах по этой теме, уделяется созданию собственных моделей и использованию встроенных моделей схем в OrCAD Pspice.

На прилагаемом к книге DVD вы найдете демонстрационную версию программы OrCAD PSpice Student Edition 9, которой можно пользоваться свободно. Кроме того, на диске размещена версия OrCAD 10.5 Demo Release, с которой можно работать в течение 30 дней после установки на компьютер.

OrCAD PSpice. Анализ электрических цепей - читать онлайн бесплатно ознакомительный отрывок

Интервал:

Закладка:

Цифровые схемы в Capture

В Capture OrCAD имеется большой выбор цифровых устройств. Начнем новый проект с именем norgate и выберем Place, Part, перейдя к библиотеке eval. Начиная с компонентов 5550, 7400, 7401, …, вы увидите большой выбор цифровых компонентов, включая логические элементы И-НЕ, ИЛИ-НЕ, исключающее ИЛИ-инверторы, И-ИЛИ-инверторы, JK-триггеры, ведущие-ведомые триггеры, 2-разрядные двоичные полные сумматоры и другие. Все перечисленные устройства доступны в демонстрационной версии OrCAD.

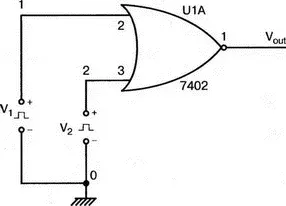

Схема ИЛИ-НЕ

В последнем примере главы 9 мы рассматривали логическую схему 7400: 2-входовую схему ИЛИ-НЕ. В качестве источников V 1и V 2были использованы источники напряжения типа PWL с выходным напряжением в виде последовательностей импульсов, представляющих уровни логических нулей и единиц. Эта схема может быть введена и в Capture OrCAD, как показано на рис. 17.32. Чтобы создать V 1и V 2, выберем компонент типа VPWL. Вспомним, как были описаны два источника в примере из главы 9:

V1 1 0 PWL(0s 0V 0.1ms 1V 1s 1V 1.0001S 0V

+ 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V 5s 1V)

V2 2 0 PWL((0s 0V 1.5s 0V 1.50001s 1V 2.5s 1V 2.50001s 0V

+ 3.5s 0V 3.50001s 1V 3.70001s 0V 5s 0V)

Рис. 17.32. Схема для исследования логического элемента И-НЕ

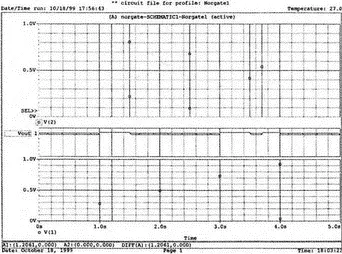

Войдя в Capture, дважды щелкните на компоненте V1 и в появившемся окне Property Editor введите следующие пары время-напряжение: «0s 0V 0.1ms 1V 1s 1V 1.0001s 0V 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V». Отметим, что в Capture можно ввести только 10 пар время-напряжение, в то время как в PSpice их число не ограничено. Дважды щелкните на компоненте V2 и введите следующие пары время-напряжение: «0s 0V 1,5s 0V 1,50001s 1V 2,5s 1V 2,50001s 0V 3,5s 0V 3,50001s 1V 3,7s 1V 3,70001s 0V 5s 0V». Завершите схему, выбрав Place, Net Alias для узлов 1, 2 и V out. Сохраните схему и подготовьте в PSpice новое моделирование с именем Norgate1. Выберите анализ переходных процессов на интервале t= 5 мс с максимальным размером шага в 1 мс. Проведите анализ и получите в Probe графики V(1) и Vout, a V(2) — на отдельном графике, как показано на рис. 17.33. Курсор на рисунке показывает, что при t =1,2 с, когда и V(1) и V(2) равны логическому нулю, выход V out равен логической единице. Уровни для обоих входных напряжений на этом графике совпадают с сеткой, что несколько затемняет картину.

Рис. 17.33. Диаграммы входных к выходного напряжений для элемента И-НЕ

Небольшая часть выходного файла показана на рис. 17.34. Интереснее всего проследить, как входные напряжения задаются в соответствующих командах. В состав этой схемы входят как аналоговые, так и цифровые схемы, аналоговые источники VPWL подключены к логическому элементу И-НЕ 7402. Это заставляет программу PSpice создавать набор аналого-цифровых интерфейсов, что вносит в простой проект излишние осложнения.

**** 09/06/99 14:20:30 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profiles Norgate1

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.TRAN 0 5s 0 1ms

.PROBE

*Netlist File:

.INC "norgate-SCHEMATIC1.net"

*Alias File:

**** INCLUDING norgate-SCHEMATIC1.net ****

* source NORGATE

V_V2 2 0

+PWL 0s 0V 1.5s 0V 1.50001s 1V 2.5s 1V 2.50001s 0V 3.5s 0V 3.50001s 1V 3.7s 1V

+ 3.70001s 0V 5s 0V V_V1 1 0

+PWL 0s 0V 0.1ms 1V 1s 1V 1.0001s 0V 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V

+ 4.0001s 1V

X_U1A 1 2 VOUT $G_DPWR $G_DGNV 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

**** RESUMING norgate-SCHEMATIC1-Norgate1.sim.cir ****

.INC "norgate-SCHEMATIC1.als"

**** INCLUDING norgate-SCHEMATIC1.als ****

.ALIASES

V_V2 V2(+=2 -=0 )

V_V1 V1(+=1 -=0 )

X_U1A U1A(A=1 B=2 Y=VOUT VCC=$G_PWR GND=$G_DGND )

**** Generated AtoD and DtoA Interfaces ****

Рис. 17.34. Выходной файл для логического элемента ИЛИ-НЕ

Схема полусумматора

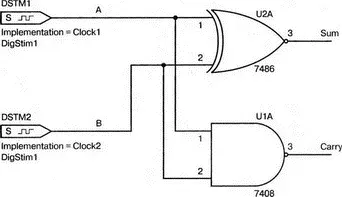

На самом деле нет необходимости использовать источник типа VPWL, чтобы обеспечить входные импульсы для цифровой схемы. Начните новый проект, использующий имя half. Библиотека Sourcestm содержит компонент DigStim1, условное обозначение которого показано на рис. 17.35, наряду с двумя другими компонентами из библиотеки eval : 2-входовой схемой исключающего ИЛИ 7486 и 2-входовой схемой И 7408. К выходу каждой из логических схем подключен короткий отрезок провода. Выходу компонента 7486, присвоен псевдоним «Sum», а выходу компонента 7408 — псевдоним «Carry».

Рис. 17.35. Схема полусумматора

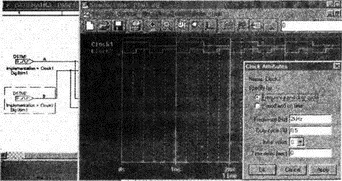

Выберите цифровую форму выходного напряжения под заголовком (А) с помощью Edit, PSpice Stimulus, New Stimulus, Digital, Clock, чтобы ввести цифровой таймер с именем Clock1. Установите параметры: частота 1 кГц, коэффициент заполнения 0,5, начальное значение 1 и нулевое запаздывание.

Закройте редактор Stimulus и, модифицировав схему, сохраните изменения. Выберите теперь цифровую форму выходного напряжения под заголовком (В) с помощью Edit, PSpice Stimulus, New Stimulus, Digital, Clock, чтобы ввести цифровой таймер с именем Clock2. Он должен иметь параметры f =2 кГц, коэффициент заполнения 0,5, нулевое начальное значение и нулевое запаздывание. Редактор Stimulus отображает форму выходного сигнала для двух таймеров, как показано на рис. 17.36.

Рис. 17.36. Редактор Stimulus, показывает входные сигналы Clock1 и Clock2

Подготовьте моделирование на PSpice с именем Half1. Выполните анализ переходных процессов на интервале в 2 мс с максимальным размером шага в 2 мкс. Проведите анализ и получите в Probe графики сигналов А, В, Sum, Carry (рис. 17.37). Если использовать курсор, то уровни этих сигналов будут показаны как единицы или нули. Как показано на рисунке, при t =1,4 мс получаются значения: А =1, В= 1 , Sum =0 и Carry =1. Часть выходного файла показана на рис. 17.38. При таком формировании входных сигналов не возникает необходимости в создании интерфейсов перехода от аналоговых к цифровым сигналам и обратно, так как используются только цифровые сигналы. В перечне элементов через U обозначаются компоненты с цифровым выходом, а через X — подсхемы.

Рис. 17.37. Входные и выходные сигналы для полусумматора

**** 10/18/99 21:28:59 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: Half1

*Libraries:

* Local Libraries :

.STMLIB ".\HALF.stl"

* From [PSPICE NETLIST] section of pspiceev.ini file:

Интервал:

Закладка: