Стивен Барретт - Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С

- Название:Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С

- Автор:

- Жанр:

- Издательство:Издательский дом «ДМК-пресс»

- Год:2007

- Город:Москва

- ISBN:5-9706-0034-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Стивен Барретт - Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С краткое содержание

В книге последовательно рассматриваются все этапы создания встраиваемых систем на микроконтроллерах с применением современных технологий проектирования. Задумав эту книгу, авторы поставили перед собой задачу научить читателя искусству создания реальных устройств управления на однокристальных микроконтроллерах.

Издание содержит материал, охватывающий все вопросы проектирования, включает множество заданий для самостоятельной работы, примеры программирования, примеры аппаратных решений и эксперименты по исследованию работы различных подсистем микроконтроллеров.

Данная книга является прекрасным учебным пособием для студентов старших курсов технических университетов, которые предполагают связать свою профессиональную деятельность с проектированием и внедрением встраиваемых микропроцессорных систем. Книга также будет полезна разработчикам радиоэлектронной аппаратуры на микроконтроллерах.

Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Рис. 9.26.Формат регистра CBTR1

Биты от 0 до 3 (TSEG13, TSEG12, TSEG11, и TSEG10) используются, чтобы установить длительность time segment 1, в соответствии с табл. 9.2. Биты от 4 до 6 (TSEG22, TSEG21 и TSEG20) используются, чтобы конфигурировать время time segment 2, как показано в табл. 9.3. Бит SAMP определяет, будет ли использоваться одна или три выборки, чтобы измерить принимаемый бит сообщения. Если бит SAMP установлен, используются три выборки, если он очищен, то только одна. Регистр CBTR1 может изменяться только при установленном бите SFTRES в регистре CMCR0.

| TSEG13 | TSEG12 | TSEG11 | TSEG10 | time segment 1 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 квант времени |

| 0 | 0 | 0 | 1 | 2 кванта времени |

| 0 | 0 | 1 | 0 | 3 кванта времени |

| 0 | 0 | 1 | 1 | 4 кванта времени |

| … | … | … | … | … |

| 1 | 1 | 1 | 1 | 16 квантов времени |

Таблица 9.2.Конфигурация длительности time segment 1

| TSEG22 | TSEG21 | TSEG20 | time segment 2 |

|---|---|---|---|

| 0 | 0 | 0 | 1 квант времени |

| 0 | 0 | 1 | 2 кванта времени |

| 0 | 1 | 0 | 3 кванта времени |

| 0 | 1 | 1 | 4 кванта времени |

| … | … | … | … |

| 1 | 1 | 1 | 8 квантов времени |

Таблица 9.3.Конфигурация длительности time segment 2

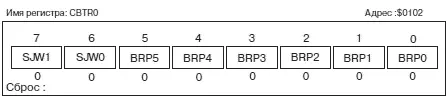

Вернемся теперь к битам 7 и 6 регистра CBTR0. При синхронизации битов на шине, используются биты скачка ресинхронизации (SJW1:SJW0), позволяющие уменьшить или увеличить ширину скачка ресинхронизации (число квантов времени). Таблица 9.4 показывает ширину скачка ресинхронизации, соответствующую различным значениям SJW1:SJW0.

| SJW1 | SJW0 | Ширина скачка ресинхронизации |

|---|---|---|

| 0 | 0 | 1 квант времени |

| 0 | 1 | 2 кванта времени |

| 1 | 0 | 3 кванта времени |

| 1 | 1 | 4 кванта времени |

Таблица 9.4.Выбор ширины скачка ресинхронизации

В заключение покажем дополнительную аппаратную возможность контроллера msCAN12 контроллера. Когда контроллер принял или передал корректное сообщение, генерируется импульс с длительностью, равной времени передачи одного бита. Этот импульс может быть послан на встроенный модуль таймерного интерфейса (TIM). Чтобы установить эту внутреннюю связь, используется бит TLNKEN в регистре CMCR0. Такое решение обеспечивает программисту необходимую гибкость. Модуль таймерного интерфейса может быть запрограммирован на определенное действие при появлении любого кадра приема или передачи, например, для каждого кадра может создаваться своя собственная метка времени.

9.3.4. Конфигурирование модуля msCAN12 для работы в сети

В этом разделе мы объединим три подсистемы контроллера msCAN12 в единое целое и покажем последовательность действий по его инициализации.

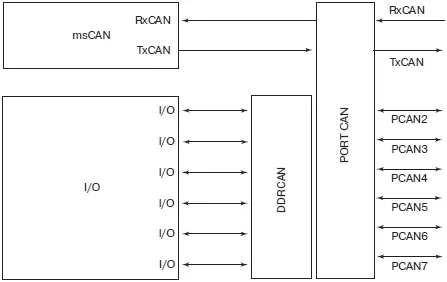

До начала нашего обсуждения конфигурации сети, отметим, что шесть из восьми выводов физического порта CAN могут использоваться как универсальные входы/выходы порта общего назначения PORTCAN. На рис. 9.27 показано использование порта CAN для таких целей. Когда выводы со 2 по 7 находятся в режиме универсальных линий ввода/вывода, следующие три регистра используются для записи и чтения данных с порта PORTCAN: регистр данных PORTCAN, регистр направления передачи DDRCAN, регистр управления PCTLCAN.

Рис. 9.27.CAN портовая конфигурация

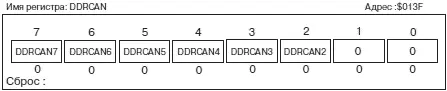

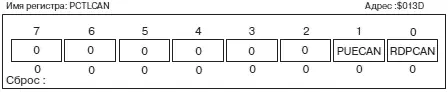

Регистр DDRCAN используется, чтобы программировать соответствующие выводы как входные или выходные. На рис. 9.28 показано назначение каждого бита регистра. Обратите внимание, что биты 0 и 1 зарезервированы как биты передачи и приема контроллера CAN и не могут быть использованы как универсальные выводы входов/выходов. Установка бита направления передачи данных в состояние логической 1 конфигурирует соответствующий вывод как выходной; установка его в состояние логического нуля — как входной. Регистр PCTLCAN, формат которого представлен на рис. 9.29, используется, чтобы разрешать или запрещать перевод выводов от 2 до 7 порта CAN в режим драйверов высокого или низкого уровня. Бит PUECAN используется, разрешать (при переводе в состояние логической 1) или запрещать (при переводе в состояние логического 0) режим драйвера высокого уровня. Бит RDPCAN выбирает конфигурацию, разрешающую (при переводе в состояние логической 1) или запрещающую (при переводе в состояние логического 0) режим драйвера низкого уровня.

Рис. 9.28.Формат регистра направления передачи DDRCAN

Рис. 9.29.Формат регистра управления PCTLCAN

И наконец, регистр PORTCAN содержит фактические данные (логические уровни) посылаемые или получаемые физическими выводами порта CAN. На рис. 9.30 показано содержимое регистра. В соответствии с установками в регистре DDRCAN, каждый бит используется передачи или приема данных из внешней среды. Обратите внимание, что, даже если модуль CAN конфигурирован для связи с сетью CAN, этот регистр будет передавать или принимать данные, в зависимости от состояния битов 1 и 0 этого регистра.

Процедура полной установки.Далее мы приведем процедуру полной установки, позволяющей конфигурировать модуль msCAN12 для связи на сетью CAN. Мы обсудим также использование прерываний, связанных модулем CAN.

Два физических внешних вывода, RxCAN и TxCAN, используются для связи с сетью. Выводы RxCAN и TxCAN соответствуют битам 0 и 1 регистра PORTCAN. Приемопередатчик CAN, который используется, чтобы управлять логическими состояниями на сетевой шине, должен быть связан с двумя выводами и должен в свою очередь быть подключен к сети CAN. Типичными примерами таких приемопередатчиков являются микросхема MC33388 или PCA82C250.

После того, как 68HC12 будет правильно подключен к сети CAN, необходимо обеспечить правильную процедуру инициализации, позволяющую установить модуль msCAN12. Обсудим эту процедуру. Прежде, чем предпринять любые шаги по инициализации, модуль msCAN12 должен быть помещен в состояние мягкого сброса, путем установки в состояние логической 1 бита SFTRES (бит 0 регистра CMCR0). Как только бит SFTRES установлен, ЦП может задать рабочую конфигурацию msCAN12, с помощью следующих регистров, связанных с CAN:

• При сбросе значение по умолчанию в регистре CMCR0 равно $21, при этом устанавливаются биты CSWAI и SFTRES. По умолчанию также очищаются биты TLNKEN и SLPRQ. Модуль msCAN12 находится в состоянии мягкого сброса и готов к работе в нормальном режиме. Вход таймера связан с портом и модуль конфигурирован таким образом, чтобы в режиме ожидания отсутствовали импульсы синхронизации.

Читать дальшеИнтервал:

Закладка: