Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]

- Название:Искусство схемотехники. Том 3 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002954-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредотачивается на тонких аспектах проектирования и применения электронных схем.

На русском языке издается в трех томах. Том 3 содержит сведения о микропроцессорах, радиотехнических схемах, методах измерения и обработки сигналов, принципах конструирования аппаратуры и проектирования маломощных устройств, а также обширные приложения.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 3 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

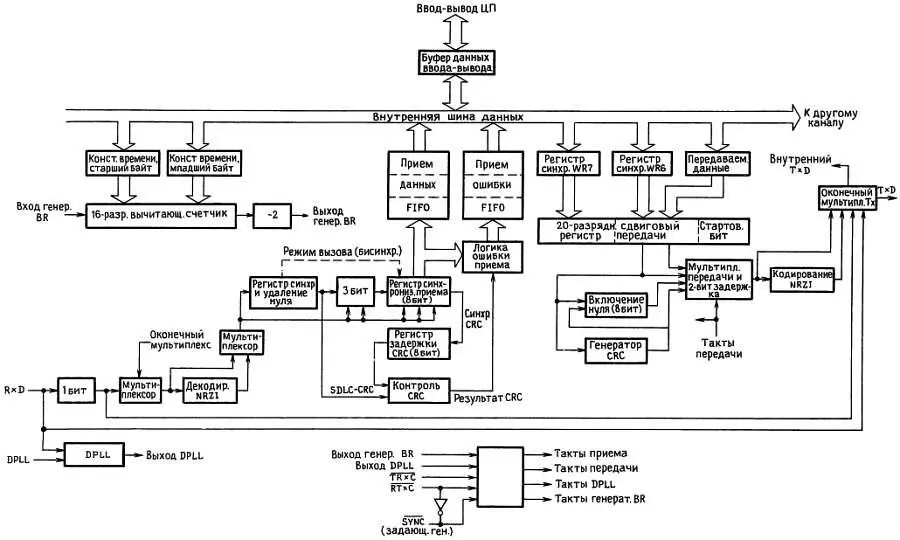

Последовательный и параллельный порты. Типичными представителями перифейрийных БИС являются микросхемы Zilog 8530 SCC (последовательный порт) и 8536 СIO (параллельный порт и таймер). Такого рода микросхемы отличаются необычной гибкостью и умопомрачительным количеством рабочих режимов, программируемых путем засылки управляющих байтов во внутренние регистры. Некоторые из этих микросхем по сложности приближаются к микропроцессорам (см. рис. 11.13), и чтобы научиться программировать их работу, вам придется затратить немало времени.

Рис. 11.13. Структурная схема последовательного порта Zilog 8530.

Примечание: BR— запрос шины; FIFO— «пеpвым вошел, первым вышел»; TxD— сигнал передачи; RxD— сигнал приема; NRZ1— кодирование без возвращения к нулю с инверсией; CRC— контроль циклическим избыточным кодом; DPLL— фазовая автоподстройка частоты; SDLC— синхронное управление линиями передачи данных.

Хотя периферийные БИС обычно разрабатываются под конкретные микропроцессоры, общность их характеристик позволяет использовать микросхемы, предназначенные для поддержки определенного семейства микропроцессоров, с процессорами других фирм. Микросхемы Zilog 85хх претендуют на роль универсальных, «магистрально-независимых» периферийных устройств, хотя при использовании их с МП 68008 возникает некоторая несовместимость в отношении строба RD ' , которую мы снимем, образовав задержанный строб RD ' .

Рассмотрим сначала параллельный порт/таймер 8536. В нем используется пара стробирующих сигналов RD ' и WR ' , а также сигнал разрешения входа СЕ ' (который, как и обычно, поступает с выхода дешифратора адреса). Кроме того, на соответствующий вход микросхемы подаются тактовые сигналы для синхронизации таймера и управления внутренней логикой. Микросхема 8536 включает цепи полностью векторизуемых прерываний с подтверждением, выставляющие вектор на линии данных в течение цикла подтверждения прерывания. Реализация всех этих излишних для нас возможностей требует использования приоритетной цепочки, связывающей устройства (с помощью входного сигнала IEi и выходного IEO), а также входа INTACK ' , управляющего установкой (программируемого) вектора. Мы же ограничимся выходным сигналом INT' для организации запроса прерывания. Из состава интерфейсной шины к параллельному порту подключаются линии данных D0-D7, а также адресные линии (А0, А1) для адресации внутренних регистров; использование двух младших адресных линий приводит к отображению внутренних регистров на адресное пространство, начинающееся с базового адреса. В нашем случае внутренние регистры располагаются по адресам $84000-$84003.

Число адресных выводов наводит на мысль, что в микросхеме имеются 4 внутренних регистра, что, однако, весьма далеко от истины: фактически порт содержит 41 регистр для записи и 48 регистров для чтения! (Мы же предупреждали, что программирование этих микросхем — кошмарное занятие!) Для доступа к регистрам вы сначала записываете в «управляющий» регистр по адресу база + 3 ($84003) байт, содержащий адрес требуемого регистра данных, а затем читаете из или записываете в выбранный регистр. В отличие от этого регистры данных параллельного порта допускают непосредственную адресацию, и в них записывают или из них читают прямо по адресам база, база + 1 и база + 2.

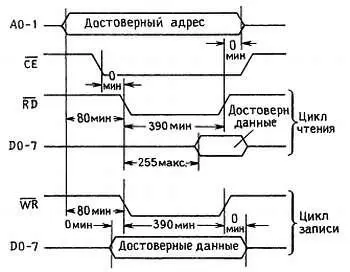

На рис. 11.14 показаны временные диаграммы циклов чтения и записи, позволяющие рассмотреть проблемы синхронизации строба RD ' .

Рис. 11.14. Синхронизация параллельного порта Zilog 8536.

Спецификации микросхемы 8536 дают минимальное значение интервала между установкой адресных сигналов А0-А1 и фронтом строба RD ' (время упреждения) 80 нc. В спецификациях также определяется время отклика, как обычно, довольно большое — бедняге 8536 требуется 255 нc для выдачи данных; длительность же сигнала RD' должна составлять 390 нc (минимум). С большим временем отклика мы уже умеем бороться с помощью состояний ожидания. Однако состояния ожидания не решат проблему с временем упреждения адреса по отношению к RD ' (из рис. 11.4 видно, что сигнал DS ' может появиться всего лишь через 30 нc после установки правильного адреса). Чтобы все работало правильно, мы должны задержать RD' на один такт ЦП: это легко сделать с помощью того же сдвигового регистра, который генерирует сигнал DTACK ' . Мы просто образуем логическое И «быстрого» строба RD ' и (инвертированного) выходного сигнала Q 0 сдвигового регистра, который не устанавливается до перепада тактового сигнала ЦП между состояниями S3 и S4. В результате образуется задержанный строб RD ' (который мы назвали DELRD ' ), начинающийся на один такт позже (в тот же момент, что и нормальный DS ' цикла записи). Описанная процедура предоставляет порту дополнительные 125 нc для упреждения адреса (в сумме 155 нc). Генератор состояний ожидания по-прежнему вводит два состояния ожидания, что делает полную длину цикла достаточной для медленных периферийных устройств.

К счастью, для сигнала WR ' не требуется аналогичная схема, потому что МП 68008 предусмотрительно увеличивает время упреждения на один такт для циклов записи (обратите внимание на задержку сигнала DS ' в цикле записи на рис. 11.4), а для микросхемы 8536 требуется то же значение времени упреждения (80 нc, см. рис. 11.14).

Интерфейс последовательного порта 8530 выглядит почти так же. Отличие заключается лишь в том, что адресные входы, выбирающие внутренние регистры, называются по-другому. Сигнал А0 подается на вход А/В ' (выбирающий канал А или В сдвоенного порта), а сигнал А1 — на вход D/C ' (который выбирает регистры данных или управления). Эта микросхема тоже не обижена регистрами: в ней имеются в каждом канале 16 регистров для записи и 9 регистров для чтения; доступ к ним осуществляется так же, как и в микросхеме 8536, в два этапа.

Тактовая частота 8530 может достигать 6 МГц; мы выбрали частоту 4 МГц, которая позволяет установить скорость передачи до 9600 бод. Асинхронные линии данных TxD и RxD работают с уровнями ТТЛ-логики, а не с биполярными сигналами стыка RS-232 (см. разд. 9.14 и 10.19 ). Большинство драйверов стыка RS-232 (например, классическая микросхема 1488) требуют двух источников питания, что для нашей системы, которая целиком питается от единственного источника +5В, будет как бельмо на глазу. К счастью, сейчас доступны искусные микросхемы, содержащие емкостные преобразователи напряжения. Эта методика была предложена фирмой Maxim в серии микросхем МАХ232; она используется также в микросхемах LT1080 фирмы LTC. Заметьте, что выход запроса прерывания с открытым стоком объединен по схеме проводного ИЛИ с соответствующим выходом микросхемы календаря-часов, так что возбуждение любого выхода приводит к автовекторизуемому прерыванию уровня IPL1. Обработчик прерывания этого уровня должен определить источник прерывания с помощью процедуры опроса, выполняя программное чтение регистра состояния каждого устройства. Соответствующая программа будет описана ниже.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]](/books/607005/paul-horovits-iskusstvo-shemotehniki-tom-3-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)