Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]

- Название:Искусство схемотехники. Том 3 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002954-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредотачивается на тонких аспектах проектирования и применения электронных схем.

На русском языке издается в трех томах. Том 3 содержит сведения о микропроцессорах, радиотехнических схемах, методах измерения и обработки сигналов, принципах конструирования аппаратуры и проектирования маломощных устройств, а также обширные приложения.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 3 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

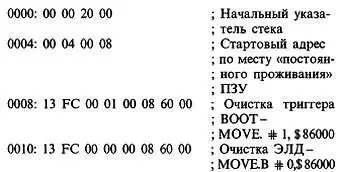

Первые 8 байт ПЗУ остроумно запрограммированы так, что осуществляется переход на продолжение программы начальной загрузки, но уже в старшем адресном пространстве, где (среди прочего) очищается порт ЭЛД (адрес $86000). Запись в порт ЭЛД имеет побочный эффект сброса триггера BOOT, в результате чего временный образ ПЗУ в начале адресного пространства замещается образом ОЗУ. Для пояснения сказанного, ниже приведено содержимое первых 24 байт ПЗУ, реализующих описанную процедуру:

Заметьте, что две последние команды выполняются по адресам $40008 и $40010 соответственно благодаря стартовому адресу, извлеченному из ячейки $0004. Подключение микросхемы ОЗУ 8Кx8 осуществляется очень просто. ОЗУ воспринимает младшие 13 бит адреса (8К) и активизируется, когда сигнал А19 снят и ПЗУ отключено. Стробирующие сигналы RD ' и WR ' подключены ко входам разрешения выхода (OE ' ) и разрешения записи (WE ' ) соответственно. Будем пока считать, что схема декодирования, обозначенная на рис. 11.10 пунктиром, отсутствует. Тогда ОЗУ располагается в самом низу адресного пространства, за исключением момента начальной загрузки, когда оно замещается временным образом ПЗУ.

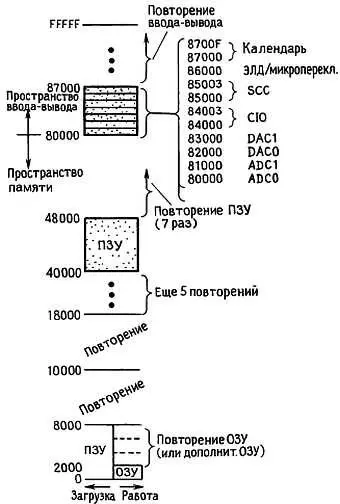

Однако наша схема декодирования адресов работает странным образом. Взглянем внимательно на ОЗУ. Мы игнорировали биты адреса А13-П17! В результате байт памяти с адресом, например $0000, имеет много двойников — его можно найти по адресам $2000, $4000 и вообще по любому адресу, имеющему нули в разрядах А0-А12 и А18-А19. Байт имеет множественное представление в адресном пространстве. Чтобы устранить эту неоднозначность, можно было более узко квалифицировать сигнал CS ' , разрешающий работу ПЗУ, обусловив нулевое состояние бит А13-А17, но в этом нет особого смысла. Хотя наличие «призраков» памяти по всему адресному пространству может показаться свидетельством небрежности, но вреда в этом нет, и к тому же экономятся вентили. То же происходит с ПЗУ (а также и с вводом-выводом). На рис. 11.11 показана карта памяти [1] Более точно — карта распределения адресного пространства. — Прим. перев .

нашего прибора, где описанные повторения обозначены явным образом.

Рис. 11.11. Карта памяти.

Разумеется, если вы захотите установить в системе дополнительную память, вам придется привлечь дополнительные адресные линии. На рис. 11.10 показано, как это можно сделать — просто подключите дешифратор 1 из 4 (`139) к двум следующим адресным линиям, активизируя его нашим сигналом разрешения ПЗУ, и без всяких хлопот вы можете добавить три блока ОЗУ. Дальнейшее расширение памяти осуществляется аналогично.

Упражнение 11.5.С помощью дешифратора 1 из 8 (`138) подключите к системе 8 блоков памяти 8Кx8.

Упражнение 11.6.Модифицируйте схему с целью подключения ОЗУ емкостью 32Кx8.

Упражнение 11.7.Теперь измените схему так, чтобы в ней работали два блока ПЗУ емкостью 64Кx8 (27512).

Упражнение 11.8.Для каждого из предыдущих упражнений нарисуйте карту памяти.

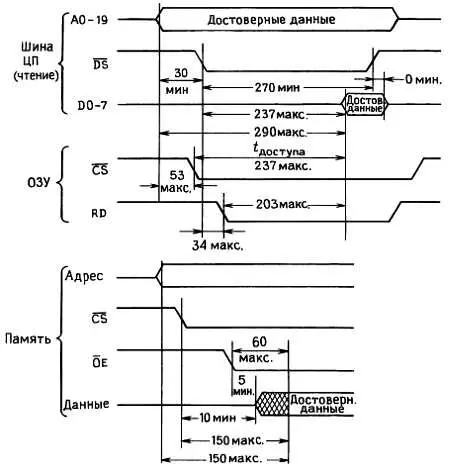

Синхронизация памяти. Перед тем, как приступать к рассмотрению ввода-вывода, полезно обратиться к вопросу синхронизации памяти. Ранее отмечалось, что наша схема генерации сигнала DTACK не создавала состояний ожидания при обращении к памяти. Это очень хорошо, но лишь в том случае, когда память обладает достаточным быстродействием, чтобы удовлетворить временным ограничением циклов чтения и записи на рис. 11.4. Но так ли это в действительности? Чтобы получить ответ на этот вопрос, надо начать с временной диаграммы МП 68008, затем вычесть наихудшие значения задержек «склеивающих» схем и посмотреть, сколько времени остается на реакцию памяти. Давайте проделаем это.

На рис. 11.12 изображен цикл чтения, для которого синхронизация обычно имеет большее значение.

Рис. 11.12. Временные соотношения цикла чтения из памяти (статическое ОЗУ, 150 нc).

Мы начали с временных характеристик ЦП для микросхемы в тактовой частотой 8 МГц, поскольку для нашей схемы мы выбрали именно эту частоту. Наиболее важным является временной интервал между правильным адресом ЦП и правильными данными памяти, так как этот интервал определяет максимально допустимое значение «времени доступа к адресу» со стороны памяти. В этом случае ЦП устанавливает правильный адрес по меньшей мере за 290 нc перед установкой правильных данных; соответствующее значение для DS ' составляет 237 нc. Наша схема образования сигнала CS ' для ОЗУ включает два каскада вентилей. При использовании микросхем 74НСТ02 и 74НСТ00 максимальные задержки составят 28 нc и 25 нc, что дает примерное значение 53 нc. В этом случае для времени доступа со стороны памяти (относительно фронта CS ' ) остается 290 нc — 53 нc = 237 нc. С помощью аналогичных рассуждений (предположив, что сигнал RD ' генерируется одной микросхемой 74НСТ32) получаем, что память должна выставить данные не позже 203 нc после установки ОЕ ' . На рис. 11.12 также показаны наихудшие временные соотношения для самой медленной (150 нc) статической памяти (ОЗУ) с организацией 8Кx8: время доступа от фронта адреса 150 нc, от фронта CS ' 150 нc и от фронта ОЕ ' 60 нc. Поскольку для нашей схемы допустимы значения 290 нc, 237 нc и 203 нc, соответственно, мы имеем для наиболее критичной ситуации (время доступа от CS ' ) запас почти 100 нc.

Мы не будем останавливаться на аналогичных рассуждениях для цикла записи, который в этом отношении является еще менее критичным. Очевидно, что с ОЗУ не возникает трудностей синхронизации, даже при использовании самой медленной памяти и при отсутствии состояний ожидания ЦП.

К сожалению, того же нельзя сказать про ПЗУ, которые обычно оказываются медленнее ОЗУ. Например, выпускаемые РПЗУ 32Кx8 характеризуются стандартными значениями времени (от адреса до данных или от CS ' до данных) 150 нc, 200 нс и 250 нc. Приведенные выше выкладки сохраняют свое значение, но надо увеличить задержку C S' на 6 нс, так как изменяется логика образования этого сигнала. В результате только два более быстрых варианта РПЗУ удовлетворяют условию максимальной задержки 231 не от CS ' до данных и могут использоваться в нашей схеме при отсутствии состояний ожидания. Вместо того, чтобы отбирать быстрые ПЗУ, можно было поставить более быструю «склеивающую» логику, например, 74АСТ или 74F; это дало бы возможность использовать ПЗУ с временем 250 нс. В действительности эти ПЗУ скорее всего будут работать в нашей схеме при любой логике, поскольку вычисления, выполненные на основе предельных временных характеристик, обычно дают результаты с большим запасом. Предельные значения достигаются при наихудшем сочетании температуры, напряжения питания, емкостной нагрузки и качества конкретной микросхемы; наши наихудшие условия предполагали значение напряжения питания 4,5 В, температурный диапазон от —40 °C до +85 °C, и неестественно высокую емкостную нагрузку 50 пФ. Если, однако, вы хотите быть уверенным в надежной работе аппаратуры, особенно в случае выпуска крупных серий приборов, следует вести расчеты по предельным значениям.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]](/books/607005/paul-horovits-iskusstvo-shemotehniki-tom-3-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)