Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Конструктивно выделяется шина ACCESS.Bus (внешняя), в которой определены разъемы и кабели, а также питание (5 В) устройств от шины; в других — нет.

Протокольные различия более существенны, из них отметим лишь следующие.

♦ В шине ACCESS.Bus определены лишь передачи данных ведущим устройством, в остальных шинах ведущее устройство может и принимать данные.

♦ В шинах ACCESS.Bus и SMBus ведущее устройство не имеет права повторного захвата шины ранее, чем через 50 мкс после начала передачи. Сигнал SCLв этой шине может удерживаться на низком уровне не дольше 2 мс. В I²C таких ограничений нет.

♦ В шине SMBus ведущее устройство ожидает от ведомого устройства немедленного ответа, в шине ACCESS.Bus ответ приходит независимо, но ожидается не позже чем через 40 мс. В шине SMBus и ведущее устройство, и ведомое устройство могут притормаживать обмен на уровне приема битов, что позволяет им вписываться в свои временные диаграммы (успевать «просыпаться», обрабатывать прерывания).

11.2. Шина управления SMI интерфейса MII

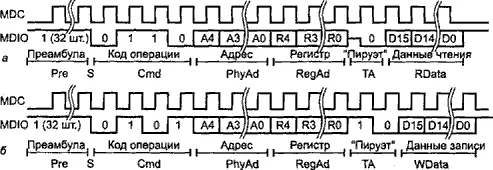

В спецификации IEEE 802.3u сетевой технологии Ethernet от 1995 г. появился интерфейс MII (Media Independent Interface — интерфейс, независимый от среды передачи), позволяющий отделять специфические устройства физического уровня (PHY) от вышестоящих уровней. Кроме интерфейса передачи «полезных» данных сети в MII входит последовательный интерфейс SMI (Serial Management Interface), обеспечивающий доступ к внутренним регистрам PHY. Эти регистры позволяют отслеживать состояние PHY и управлять им; в частности, и управлять согласованием режимов сетевых портов. В спецификации описаны регистры, обязательные для устройств, а также отведено место для специфических регистров, используемых по воле разработчика. Интерфейс SMI представляет собой последовательную синхронную трехпроводную шину (сигналы MDC, MDIOи шина GND), обеспечивающую доступ по записи и чтению к 16-разрядным регистрам устройств. Протокол шины обеспечивает 5-битную адресацию подключаемых устройств, что позволяет непосредственно объединять до 32 устройств на одной шине. Каждое устройство может иметь до 32 регистров. Шина является хост-центрической — ею управляет один контроллер, инициирующий транзакции, а все подключаемые устройства являются ведомыми. Контроллер генерирует импульсы синхронизации по однонаправленной линии MDC, а по двунаправленной линии MDIOформирует биты команд и данных (при записи) и принимает данные чтения. Устройство, опознавшее свой адрес, должно выполнить адресуемую ему команду. Уровни сигналов — обычные для логики ТТЛ и КМОП; для линии MDIOобычно используются формирователи с открытым коллектором (стоком) и резисторы, «подтягивающие» пассивную линию к уровню питания (+5 или +3,3 В). Частота импульсов MDC, не обязательно постоянная, не должна превышать 2,5 МГц, что позволяет реализовать функции контроллера чисто программно. Временны́́е диаграммы сигналов для транзакций чтения и записи приведены на рис. 11.4. Отметим, что устройство должно фиксировать биты по положительному перепаду MDC, а контроллер фиксирует биты по отрицательному перепаду. Адреса и данные передаются начиная со старших бит.

Рис. 11.4. Транзакции на шине SMI: a — запись, б — чтение

В общем случае каждой транзакции должна предшествовать преамбула Pre — не менее 32 тактов нахождения MDIOна высоком уровне. Собственно транзакция начинается с условия Start — вывода контроллером битовой последовательности «01», за которым следует двухбитная команда Cmd: «10» — чтение или «01» — запись. Далее контроллер передает 5-битный адрес устройства ( PhyAd), за которым следует 5-битный номер регистра ( RegAd). После этого следует двухбитный «пируэт» (turnaround) ТАдля перехода к передаче данных. При операции записи «пируэт» сводится к передаче контроллером последовательности «10», а затем он передает 16 бит данных ( WData) для записи в регистр. При чтении с начала «пируэта» контроллер отпускает линию MDIO, а на время второго бита отозвавшееся адресованное устройство устанавливает на этой линии нуль, что используется для определения факта ответа. В следующие 16 тактов устройство передает считанные данные ( RData) контроллеру.

Преамбула нужна только для приведения интерфейсной части устройств в исходное состояние (после подачи питания); если питание устройством не терялось, то последующие транзакции могут выполняться и без преамбулы. Имеется также нюанс в «пируэте»: для некоторых устройств второй его бит оказывается лишним — он сбивает синхронизацию данных на 1 такт.

11.3. Интерфейс SPI

Интерфейс SPI (Serial Peripheral Interface), он же Microwire, — трехпроводный синхронный с раздельными линиями входных и выходных данных — применяется для связи микроконтроллеров с периферийными микросхемами и микросхемами памяти. С его помощью программируются многие микросхемы программируемой логики (например, FPGA фирмы Altera), применяемые в различных узлах ПК и периферии. По сравнению с I²C интерфейс SPI обеспечивает более высокую скорость передачи данных. Частота синхронизации может достигать 5 МГц (зависит от подключаемых устройств); при этом за каждый такт синхронизации одновременно может и передаваться, и приниматься очередной бит данных. В основном варианте использования предполагается, что интерфейс соединяет одно ведущее устройство с одним или несколькими ведомыми устройствами. Интерфейс может применяться и для обмена между несколькими микроконтроллерами, допуская наличие на шине нескольких ведущих устройств, но протокол предоставления доступа не стандартизован. Ниже рассматривается работа интерфейса с одним ведущим устройством. В интерфейсе используются 3 обязательных сигнала:

♦ SCK(Serial Clock) — синхросигнал, которым ведущее устройство стробирует каждый бит данных;

♦ MOSI(Master Output Slave Input) — выходные данные ведущего устройства и входные данные ведомого устройства;

♦ MISO(Master Input Slave Output) — входные данные ведущего устройства и выходные данные ведомого устройства.

Кроме того, может использоваться сигнал выбора ведомого устройства SS#(Slave Select, или CS#— Chip Select): ведомое устройство должно реагировать на сигналы интерфейса и генерировать выходные данные на линии MISO только при низком уровне этого сигнала; при высоком уровне выход MISOдолжен переводиться в высокоимпедансное состояние. С помощью сигналов SS#, раздельно формируемых ведущим устройством для каждого из ведомых устройств, ведущее устройство может выбирать партнером в транзакции одно из ведомых. При этом получается гибридная топология соединений: по сигналам SCK, MOSIи MISO— топология шинная, по SS#— звездообразная (центр — ведущее устройство).

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)