Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Регистр BSRпредставляет собой длинный сдвигающий регистр, каждым битом которого являются пограничные ячейки, установленные на всех входных и выходных сигналах процессора. Для двунаправленных сигналов (или их групп), кроме собственно информационных ячеек регистра, соответствующих внешним сигналам, имеются и управляющие ячейки, задающие режим работы информационных ячеек. К примеру, у процессоров P6 длина BSRсоставляет 159 бит.

Регистр DIDдлиной 32 бита содержит идентификатор производителя, код устройства и номер версии, по которым TAP-контроллер может распознать, с каким устройством он имеет дело.

Регистр IRслужит для хранения исполняемой тестовой инструкции. Его длина зависит от тестируемого устройства. Для всех устройств обязательными являются инструкции BYPASS, IDCODE, SAMPLEи EXTEST.

Инструкция BYPASS(все биты кода — единичные) предназначена для подключения однобитного обходного регистра, обеспечивая скорейшее прохождение данных через устройство; при этом оно никак не реагирует на проходящий поток. Вход TDIобычно «подтягивают» резистором к высокому уровню, при этом разрыв цепочки JTAG приведет к подключению обходных регистров во всех устройствах после точки обрыва. Это исключает возможные непредсказуемые действия устройств в случае обрыва.

Инструкция идентификации IDCODE(младшие биты кода — 10) подключает к интерфейсу регистр DID, позволяя считать его содержимое (поступающие входные данные не могут изменить его значение).

Инструкция SAMPLE/PRELOAD(младшие биты кода — 01) имеет два назначения. Когда TAP-контроллер находится в состоянии Capture-DR (см. ниже), эта инструкция позволяет выполнить моментальный «снимок» состояния всех внешних сигналов без воздействия на работу устройства. Значение сигналов фиксируется по положительному перепаду TCK. В состоянии Update-DR по этой инструкции данные загружаются в выходные ячейки тестового порта (но еще не на выходы устройства), откуда впоследствии они будут выводиться (подаваться на выводы процессора) по инструкции EXTEST. Данные загружаются по спаду сигнала TCK.

Инструкция EXTEST(младшие биты кода — 00) предназначена для проверки внешних цепей (по отношению к тестируемому устройству). При этом на выходные выводы подаются сигналы, предварительно записанные в регистр BSR, а состояние входных сигналов фиксируется в этих регистрах. Двунаправленные сигналы предварительно конфигурируются соответствующими им управляющими битами ячеек BSR.

Стандарт 1149.1 предусматривает и инструкцию тестирования внутренней логики устройства INTEST, но ее поддерживают не все устройства.

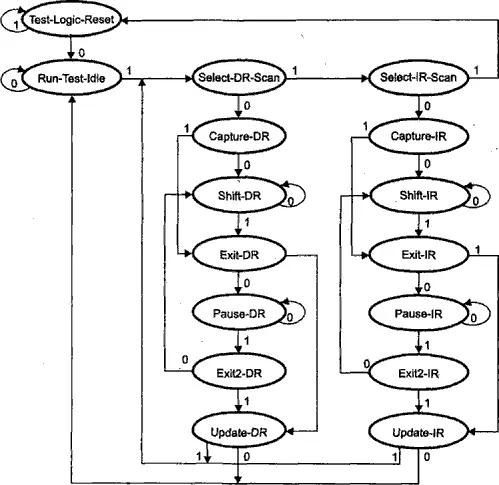

Контроллер тестового порта (TAP-controller) представляет собой синхронный конечный автомат, изменяющий состояние по фронту сигнала TCKи по включению питания. Сменой состояний управляет сигнал TMS(Test Mode State), воспринимаемый по положительному перепаду TCK. Граф состояний и переходов управляющего автомата представлен на рис. 11.8. Около стрелок переходов указаны значения сигнала TMSво время фронта TCK.

Рис. 11.8. Граф состояний и переходов контроллера TAP

В исходное состояние Test-Logic-Reset контроллер автоматически переходит по включении питания и из любого другого состояния может быть переведен высоким уровнем TMS, удерживаемым не менее пяти тактов TCK. Для перевода в состояние Test-Logic-Reset иногда используют и дополнительный сигнал TRST. В этом состоянии тестовая логика запрещена, и устройство работает в нормальном режиме.

Состояние Run-Test/Idle является промежуточным между выполнением тестовых операций. В этом состоянии регистры не изменяют своего значения.

В состоянии Capture-DR во время выполнения инструкций EXTESTи SAMPLE/PRELOADсканирующий регистр фиксирует только данные на входных линиях.

В состоянии Shift-DR данные с TDIпродвигаются через подключенный сдвиговый регистр на выход TDO.

В состоянии Pause-DR контроллер временно запрещает продвижение данных через сдвиговый регистр.

В состоянии Update-DR по спаду TCKсигналы из сдвигового регистра фиксируются на выходах тестовых ячеек.

В состоянии Capture-IR контроллер загружает в сдвиговый регистр инструкций код «безобидной» инструкции SAMPLE.

В состоянии Shift-IR в цепь между TDIи TDOвключается сдвиговый регистр инструкций, но еще исполняется предыдущая инструкция.

В состоянии Pause-IR контроллер временно запрещает продвижение данных через сдвиговый регистр инструкций.

В состоянии Update-IR по спаду TCKфиксируется новая исполняемая инструкция, и в цепь TDI- TDOвключается соответствующий ей регистр.

Кроме этих основных состояний контроллера, определяющих действия тестового оборудования, имеются и временные промежуточные состояния, необходимые для реализации переходов автомата. К ним относятся Select-DR-Scan, Exit1-DR, Exit2-DR, Select-DR-Scan, Exit1-IR и Exit2-IR .

Для интерфейса JTAG существует специальный язык описания устройств BSDL (Boundary Scan Description Language). Состав и порядок следования информационных и управляющих ячеек в сдвиговом регистре данных специфичен для каждого устройства (для чего и существует идентификационный регистр) и сообщается его разработчиками.

Интерфейс JTAG используется не только для тестирования, но и для программирования различных устройств, в том числе и энергонезависимой памяти микроконтроллеров. Контакты для сигналов JTAG имеются на шине PCI, однако в их использовании единообразия не наблюдается (либо остаются неподключенными, либо соединяются для организации цепочки). Интерфейс JTAG имеется в современных процессорах; здесь он позволяет не только тестировать сам процессор (это не представляет особого прикладного интереса), но и организовать зондовый режим отладки (probe mode, см. [6, 7]). Зондовый режим является мощным средством отладки системного программного обеспечения; обычный процессор, связанный с тестовым контроллером интерфейсом JTAG, превращается во внутрисхемный эмулятор — мечту разработчика системного ПО.

11.5. Программно-управляемая реализация последовательных интерфейсов

Рассмотренные выше интерфейсы — I²C, SMBus, SMI, SPI и JTAG — имеют общее свойство: они управляются и синхронизируются контроллером и не требуют фиксированной частоты синхронизации. Это позволяет для многих применений программно реализовать их на любом компьютере или микроконтроллере. На рис. 11.9 приведена схема простейшего адаптера интерфейсов I²C, SMBus или SMI для LPT-порта. Здесь сигнал SCL(или MDCв SMI) формируется непосредственно от выходной линии Strobe; для его переключения достаточно последовательно записывать в бит 0 регистра CR(порт с адресом LPT_BASE+2) нули (высокий уровень сигнала) и единицы (низкий). Двунаправленный сигнал SDA( MDIOв SMI) реализуется чуть сложнее: для передачи нуля в бит 1 регистра CR( LPT_BASE+2) записывается единица, для передачи единицы — нуль. На время чтения в этот бит должен быть записан нуль (чтобы на выходе был высокий уровень), данные (инверсные) считываются из бита 7 регистра SR( LPT_BASE+1). В адаптере должен использоваться диод с малым прямым падением напряжения. Лучше всего для этого подходят германиевые меза-диоды Д310 или Д311; кремниевые диоды, даже с барьерами Шоттки, здесь работают хуже (возможен слишком высокий формируемый уровень нуля).

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)