Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Возможен и иной способ общения ведущего устройства с несколькими ведомыми устройствами с чисто шинной топологией. Здесь сигнал SS#для выбора устройств не используется, но ведомые устройства все время «слушают» шину, ожидая специальной адресной посылки в начале транзакции. Опознав свой адрес, устройство отрабатывает дальнейшие протокольные посылки, и теперь ему разрешается выводить данные на линию MISOдо конца текущей транзакции. Однако этот вариант требует довольно сложной логики поведения ведомого устройства.

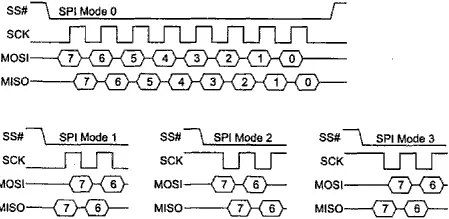

Данные передаются старшим битом вперед. Устройства различных производителей могут использовать разные режимы обмена (SPI Mode 0…SPI Mode 3), различающиеся фазой и полярностью синхросигналов. Рис. 11.5 иллюстрирует передачу и прием байта в различных режимах. Заметим, что в любом режиме входные и выходные данные стробируются по разным перепадам синхроимпульсов. Кроме того, есть варианты в использовании сигнала SS#. В первом варианте (он и представлен на рисунке) для ведомого устройства признаком начала транзакции является спад сигнала SS#, а завершения — его подъем. Во втором варианте начало транзакции определяется по первому фронту (спаду) SCK, а сигнал SS#может иметь низкий уровень постоянно. Второй вариант иногда предпочитают для простейшего двухточечного интерфейса с единственным ведущим устройством и единственным ведомым устройством, когда нет опасения потери синхронизации. Микроконтроллеры с аппаратным портом SPI, как правило, имеют возможность программного выбора режима. Форматы транзакций зависят от устройств, но общая идея такова: ведущее устройство по линии MOSIпосылает код операции и адресную информацию для устройства; затем следуют данные. В операции записи они передаются ведущим устройством по той же линии, в операции чтения устройство их посылает по линии MISO. На время всей транзакции ведущее устройство сохраняет активное состояние линии SS#, число требуемых синхроимпульсов зависит от формата команды.

Рис. 11.5. Форматы передач по интерфейсу SPI

11.4. Интерфейс JTAG

Интерфейс JTAG (Joint Test Action Group) предназначен для тестирования сложных логических схем, установленных в целевое устройство. Этот интерфейс описан в стандарте IEEE 1149.1 Boundary Scan Architecture и является последовательным синхронным, но в связи со спецификой назначения значительно отличается от вышеописанных интерфейсов, ориентированных на передачу данных. Интерфейсом JTAG управляет одно устройство-контроллер (чаще всего это ПК с соответствующим интерфейсным адаптером), к которому может быть подключено несколько тестируемых устройств. Ниже перечислены сигналы интерфейса JTAG.

♦ TCK(Test Clock) — сигнал синхронизации последовательных данных; генерируется контроллером. Частота синхронизации может достигать 16 МГц.

♦ TMS(Test Mode Select) — сигнал выбора тестового режима. Генерируется контроллером.

♦ TDI(Test Data Input) — входные данные, принимаемые устройством в последовательном двоичном коде (младшим битом вперед).

♦ TDO(Test Data Output) — выходные данные, передаваемые устройством в последовательном двоичном коде.

♦ TRST(Test Logic Reset) — необязательный сигнал сброса логики интерфейсного порта, генерируемый контроллером.

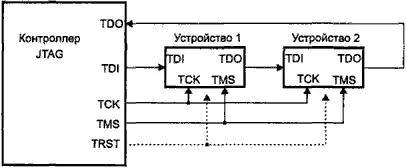

Эти сигналы (все однонаправленные), имеющие обычные логические уровни, образуют тестовый порт TAP (Test Access Port), через который тестируемое устройство подключается к тестирующему оборудованию (контроллеру). В задачу тестирующего оборудования входит формирование тестовых сигналов по программе тестирования, определенной разработчиком тестируемого устройства, и сравнение полученных результатов с эталонами. Один и тот же контроллер и порт могут использоваться для тестирования любого числа устройств, поддерживающих JTAG. Для этого устройства своими портами TAP соединяются в цепочку (рис. 11.6). Стандартизованный логический формат позволяет контроллеру независимо общаться с каждым из устройств цепочки (для этого, конечно, они должны иметь исправные ячейки JTAG).

Рис. 11.6. Цепочка устройств с интерфейсом JTAG

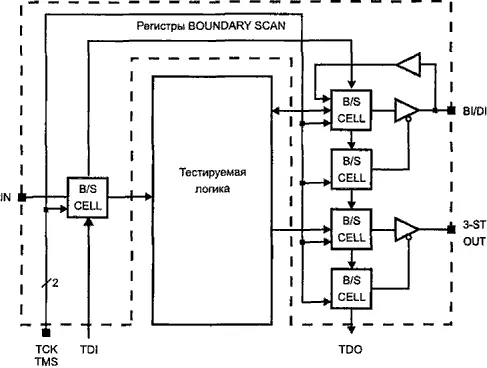

Идею тестирования любой цифровой схемы иллюстрирует рис. 11.7, на котором показана условная цифровая система, имеющая входные, выходные (возможно, с третьим состоянием) и двунаправленные сигналы. Ячейки тестирования B/S врезаются между реальными внешними выводами устройства и собственно логическим устройством, то есть располагаются на логической границе (boundary) устройства. TAP-контроллер способен сканировать ячейки — управлять ими и считывать с них информацию. Отсюда и пошло название Boundary Scan , которое можно перевести как «периферийное сканирование». При включенном тестовом режиме TAP-контроллер может логически отсоединить сигналы от внешних выводов, задавать входные воздействия и считывать результаты — собственно, это все, что необходимо для тестирования последовательностных схем (автоматов с памятью). Прелесть JTAG заключается в том, что независимо от сложности устройства оно тестируется с помощью всего лишь четырех сигналов — все сложности прячутся в достаточно простые ячейки, «окутывающие» его сигнальные выводы.

Рис. 11.7. Включение ячеек сканирования

Тестовая логика, встраиваемая в устройство, поддерживающее JTAG, состоит из следующих элементов:

♦ тестовый порт TAP (четыре интерфейсных сигнала);

♦ TAP-контроллер, управляющий тестовыми регистрами;

♦ регистр инструкций IR (Instruction Register), который принимает последовательный код со входа TDI (код инструкции используется для выбора исполняемой тестовой операции или регистра тестовых данных, к которым производится обращение);

♦ регистры тестовых данных, из которых любое устройство должно иметь три обязательных регистра: ВPR(Bypass Register), DID(Device Identification Register) и BSR(Boundary Scan Register).

Регистры инструкций и данных представляют собой независимые сдвиговые регистры, соединенные параллельно. На их входы (старшие биты) приходит сигнал TDI, с выходов (младшие биты) снимается сигнал TDO. По каждому положительному перепаду данные продвигаются на один бит.

Регистр ВРRимеет длину в один бит. Он используется как кратчайший обходной путь для последовательных данных, когда остальные регистры не участвуют в обмене.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)