Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Конфигурационное пространство устройства начинается со стандартного заголовка, в котором содержатся идентификаторы производителя, устройства и его класса, а также описание требуемых и занимаемых системных ресурсов. После заголовка могут располагаться регистры, специфичные для устройства; они могут занимать адреса конфигурационного пространства в пределах 40-FFh.

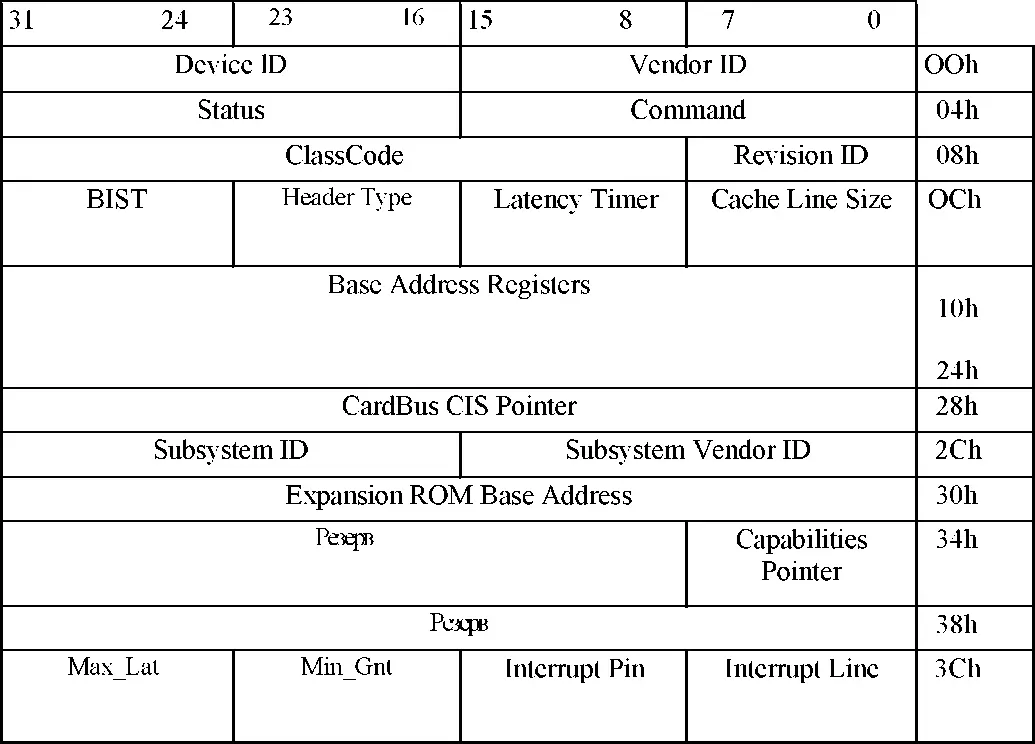

Формат заголовка приведен на рис. 6.10. Серым цветом здесь выделены поля, обязательные для всех устройств.

Рис. 6.10. Формат заголовка конфигурационного пространства устройства PCI

Перечисленные ниже поля идентификации допускают только чтение.

♦ Deviсе ID— идентификатор устройства, назначаемый производителем.

♦ Vendor ID— идентификатор производителя микросхемы PCI, назначенный PCI SIG. Идентификатор FFFFh является недопустимым; это значение должно возвращаться при чтении конфигурационного пространства несуществующего устройства.

♦ Revision ID— версия продукта, назначенная производителем. Используется как расширение поля Device ID.

♦ Header Type— тип заголовка (биты 6:0), определяющий формат ячеек в диапазоне 10-3Fh и несущий признак многофункционального устройства (если бит 7=1). На рисунке приведен формат заголовка типа 0, относящийся именно к устройствам PCI. Тип 01 относится к мостам PCI-PCI; тип 02 относится к мостам для CardBus.

♦ Class Code— код класса, определяющий основную функцию устройства, а иногда и его программный интерфейс (см. п. 6.2.13). Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

Остальные поля заголовка являются регистрами устройств , допускающими как запись, так и чтение.

♦ Command(RW) — регистр команд, управляющий поведением устройства на шине PCI. Регистр допускает как запись, так и чтение. После аппаратного сброса все биты регистра (кроме специально оговоренных исключений) обнулены. Назначение бит регистра команд:

• бит 0 — IO Space— разрешение ответа на обращения к пространству ввода-вывода;

• бит 1 — Memory Space— разрешение ответа на обращения к пространству памяти;

• бит 2 — Bus Master— разрешение работы инициатором (в режиме управления шиной);

• бит 3 — Special Cycles— разрешение реакции на специальные циклы;

• бит 4 — Memory Write and Invalidate enable— разрешение использовать команды «запись с инвалидацией» при работе инициатором (если бит обнулен, то вместо этих команд должна использоваться обычная запись в память);

• бит 5 — VGA palette snoop— разрешение слежения за записью в регистр палитр;

• бит 6 — Parity Error Response— разрешение нормальной реакции (вырабатывать сигнал PERR#) на обнаруженную ошибку паритета (если бит обнулен, то устройство должно только фиксировать ошибку в регистре состояния, в то время как генерация бита паритета устройством выполняется всегда);

• бит 7 — Stepping Control— возможность пошагового переключения (address/data stepping) линий (если устройство никогда этого не делает, бит регистра «запаян» в «0», если делает всегда — в «1», устройство с такой возможностью по сбросу устанавливает этот бит в «1»);

• бит 8 — SERR# Enable— разрешение генерации сигнала ошибки SERR#(ошибка паритета адреса сообщается, когда этот бит и бит 6=1);

• бит 9 — Fast Back-to-Back Enable(необязательный) — разрешение ведущему устройству использовать быстрые смежные обращения к разным устройствам (если бит обнулен, быстрые обращения допустимы лишь для транзакций с одним агентом);

• биты 10–15 — резерв.

♦ Status— регистр состояния, допускающий кроме чтения еще и запись. Однако запись выполняется специфично — с ее помощью можно только обнулять биты, но не устанавливать. Биты, помеченные как RO, допускают только считывание. При записи в позиции обнуляемых бит устанавливаются единичные значения. Назначение бит регистра состояния:

• биты 0–3 — резерв;

• бит 4 — Capability List(RO, необязательный) — указание на наличие указателя новых возможностей (смещение 34h в заголовке);

• бит 5 — 66 MHz Capable(RO, необязательный) — поддержка частоты 66 МГц;

• бит 6 — резерв;

• бит 7 — Fast Back-to-Back Capable(RO, необязательный) — поддержка быстрых смежных транзакций (fast back-to-back) с разными устройствами;

• бит 8 — Master Data Parity Error(только для устройств с прямым управлением) — устанавливается, когда устройство с установленным битом 6 в регистре команд, являясь инициатором, само ввело (при чтении) или обнаружило (при записи) сигнал PERR#;

• биты 10:9 — DEVSEL Timing— скорость выборки: 00 — быстрая, 01 — средняя, 10 — низкая (определяет самую медленную реакцию DEVSEL#на все команды, кроме Configuration Readи Configuration Write);

• бит 11 — Signaled Target Abort—устанавливается целевым устройством, когда оно отвергает транзакцию;

• бит 12 — Received Target Abort— устанавливается инициатором, когда он обнаруживает отвергнутую транзакцию;

• бит 13 — Received Master Abort— устанавливается ведущим устройством, когда оно отвергает транзакцию (кроме специального цикла);

• бит 14 — Signaled System Error— устанавливается устройством, подавшим сигнал SERR#;

• бит 15 — Detected Parity Error— устанавливается устройством, обнаружившим ошибку паритета.

♦ Cache Line Size(RW) — размер строки кэша (0-128, допустимые значения 2 n, иные трактуются как 0). По этому параметру инициатор определяет, какой командой чтения воспользоваться (обычное чтение, чтение строки или множественное чтение). Ведомое устройство использует этот параметр для поддержки пересечения границ строк при пакетных обращениях к памяти. По сбросу регистр обнуляется.

♦ Latency Timer(RW) — значение таймера задержки (см. п. 6.2.4) в тактах шины. Часть битов может не допускать изменения (обычно младшие три бита неизменны, так что таймер программируется с дискретностью в 8 тактов).

♦ BIST(RW) — регистр управления встроенным самотестированием. Назначение бит регистра:

• бит 7 — возможность BIST;

• бит 6 — запуск теста: запись единицы инициирует тест, по окончании устройство сбрасывает бит (тест должен быть завершен не более чем за 2 с);

• биты 5:4 — резерв (0);

• биты 3:0 — код завершения теста: 0 — тест прошел успешно.

♦ Card Bus CIS Pointer(необязательный) — указатель на структуру описателя Card Bus для комбинированного устройства PCI+Card Bus.

♦ Interrupt Line(RW) — номер входа контроллера прерывания для используемой линии запроса (0-15 — IRQ0-IRQ15, 255 — неизвестный или не используется).

♦ Interrupt Pin(RO) — контакт, используемый для запроса прерывания: 0 — не используется, 1 — INTA#, 2 — INTB#, 3 — INTC#, 4 — INTD#, 5-FFh — резерв.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)