Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

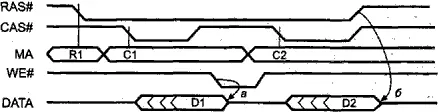

Рис. 7.4. Управление выходным буфером EDO DRAM

Из принципиального различия в работе выходных буферов следует, что в одном банке не стоит смешивать EDO и стандартные модули. EDO-модули поддерживаются не всеми чипсетами и системными платами (в большей мере это относится к системным платам для процессоров 486).

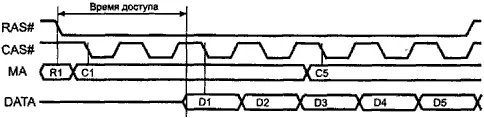

В памяти BEDO DRAM (Burst EDO) кроме регистра-защелки выходных данных, стробируемого теперь по фронту импульса CAS#, содержится еще и внутренний счетчик адреса колонок для пакетного цикла. Это позволяет выставлять адрес колонки только в начале пакетного цикла (рис. 7.5), а во 2-й, 3-й и 4-й передачах импульсы CAS#только запрашивают очередные данные. В результате удлинения конвейера выходные данные как бы отстают на один такт сигнала CAS#, зато следующие данные появляются без тактов ожидания процессора, чем обеспечивается лучший цикл чтения. Задержка появления первых данных пакетного цикла окупается повышенной частотой приема последующих. BEDO-память применяется в модулях SIMM-72 и DIMM, но поддерживается далеко не всеми чипсетами.

Рис. 7.5. Страничный режим считывания BEDO DRAM

Вышеперечисленные типы памяти являются асинхронными по отношению к тактированию системной шины компьютера. Это означает, что все процессы инициируются только импульсами RAS#и CAS#, а завершаются через какой-то определенный (для данных микросхем) интервал. На время этих процессоров шина памяти оказывается занятой, причем в основном ожиданием данных.

7.1.2. Синхронная память — SDRAM и DDR SDRAM

Микросхемы синхронной динамической памяти SDRAM (Synchronous DRAM) представляет собой конвейеризированные устройства. По составу сигналов интерфейс SDRAM близок к обычной динамической памяти: кроме входов синхронизации здесь есть мультиплексированная шина адреса, линии RAS#, CAS#, WE#(разрешение записи) и CS#(выбор микросхемы) и линии данных (табл. 7.3). Все сигналы стробируются по положительному перепаду синхроимпульсов, комбинация управляющих сигналов в каждом такте кодирует определенную команду . С помощью этих команд организуется та же последовательность внутренних сигналов RASи CAS, которая рассматривалась и для памяти FPM.

Таблица 7.3. Назначение сигналов в микросхемах SDRAM

| Сигнал | I/O | Назначение |

|---|---|---|

| CLK | I | Clock Input — синхронизация, действует по положительному перепаду |

| CKE | I | Clock Enable — разрешение синхронизации (высоким уровнем). Низкий уровень переводит микросхему в режим Power Down, Suspend или Self Refresh |

| CS# | I | Chip Select — разрешение декодирования команд (низким уровнем). При высоком уровне новые команды не декодируются, но выполнение начатых продолжается |

| RAS#, CAS#, WE# | I | Row Address Strobe, Column Address Strobe, Write Enable — сигналы, определяющие операцию (код команды) |

| BS0, BS1 или BA0, BA1 | I | Bank Selects или Bank Address — выбор банка, к которому адресуется команда |

| А[0:12] | I | Address — мультиплексированная шина адреса. В циклах Bank Activate определяют адрес строки. В циклах Read/Write линии A[0:9] и А11 задают адрес столбца. Линия А10 в циклах Read/Write включает режим автопредзаряда (при А10=1), в цикле Precharge A10=1 задает предзаряд всех банков (независимо от BS0, BS1) |

| DQx | I/O | Data Input/Output — двунаправленные линии данных |

| DQM | I | Data Mask — маскирование данных. В цикле чтения высокий уровень переводит шину данных в высокоимпедансное состояние (действует через 2 такта). В цикле записи высокий уровень запрещает запись текущих данных, низкий — разрешает (действует без задержки) |

| V SS, V DD | – | Общий провод и питание ядра |

| V SSQ, V DDQ | – | Общий провод и питание выходных буферов. Изолированы от питания ядра для снижения помех |

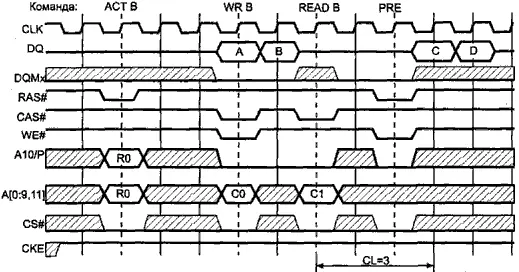

Данные для первой передачи пакета записи устанавливаются вместе с командой WR. Данные для остальных передач пакета передаются в следующих тактах. Первые данные пакета чтения появляются на шине через определенное количество тактов после команды. Это число, называемое CAS Latency (CL), определяется временем доступа T CACи тактовой частотой. Остальные данные пакета выдаются в последующих тактах. Временные диаграммы работы SDRAM приведены на рис. 7.6. Здесь показана команда записи WR, за которой следует команда чтения RDиз той же страницы, предварительно открытой командой ACT. Далее страница закрывается командой PRE. Длина пакета 2, CL = 3.

Рис. 7.6. Временные диаграммы пакетных циклов SDRAM: А и В — данные для записи по адресу R0/C0 и R0/C0+1, С и D — данные, считанные по адресу R0/C1 и R0/C1 +1

Регенерация (цикл CBR с внутренним счетчиком адреса регенерируемой строки) выполняется по команде REF, которую можно вводить только при состоянии покоя ( idle ) всех банков.

Микросхемы SDRAM оптимизированы для пакетной передачи. У них при инициализации программируется длина пакета (burst length=1, 2, 4, 8 элементов), порядок адресов в пакете (wrap mode: interleave/linear — чередующийся/линейный) и операционный режим. Пакетный режим может включаться как для всех операций (normal), так и только для чтения (Multiple Burst with Single Write). Этот выбор позволяет оптимизировать память для работы либо с WB, либо с WT-кэшем.

Обратим внимание, что внутренний счетчик адреса работает по модулю, равному запрограммированной длине пакетного цикла (например, при burst length=4 он не позволяет перейти границу обычного четырехэлементного пакетного цикла).

Пакетные циклы могут прерываться (принудительно завершаться) последующими командами. При этом оставшиеся адреса отбрасываются, и прерывающий пакет будет иметь полную длину (если его самого не прервут).

В команде Writeимеется возможность блокирования записи данных любого элемента пакета — для этого достаточно в его такте установить высокий уровень сигнала DQM. Этот же сигнал используется и для перевода в высокоимпедансное состояния буферов данных при операции чтения.

Микросхемы SDRAM имеют средства энергосбережения , для управления ими используется вход разрешения синхронизации CKE.

В режиме саморегенерации (Self Refresh) микросхемы периодически выполняют циклы регенерации по внутреннему таймеру и не реагируют на внешние сигналы, поэтому внешняя синхронизация может быть остановлена.

Режимы пониженного потребления (Power Down Mode) устанавливаются при переводе CKEв низкий уровень командой NOPили INHBT. В этих режимах микросхема не воспринимает команд. Поскольку в данных режимах регенерация не выполняется, длительность пребывания в них ограничена периодом регенерации.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)