Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия

- Название:Аппаратные интерфейсы ПК. Энциклопедия

- Автор:

- Жанр:

- Издательство:Издательский дом «Питер»

- Год:2002

- Город:Санкт-Петербург

- ISBN:5-94723-180-8

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Михаил Гук - Аппаратные интерфейсы ПК. Энциклопедия краткое содержание

Книга посвящена аппаратным интерфейсам, использующимся в современных персональных компьютерах и окружающих их устройствах. В ней подробно рассмотрены универсальные внешние интерфейсы, специализированные интерфейсы периферийных устройств, интерфейсы устройств хранения данных, электронной памяти, шины расширения, аудио и видеоинтерфейсы, беспроводные интерфейсы, коммуникационные интерфейсы, вспомогательные последовательные интерфейсы. Сведения по интерфейсам включают состав, описание сигналов и их расположение на разъемах, временные диаграммы, регистровые модели интерфейсных адаптеров, способы использования в самостоятельно разрабатываемых устройствах. Книга адресована широкому кругу специалистов, связанных с эксплуатацией ПК, а также разработчикам аппаратных средств компьютеризированной аппаратуры и их программной поддержки.

Аппаратные интерфейсы ПК. Энциклопедия - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

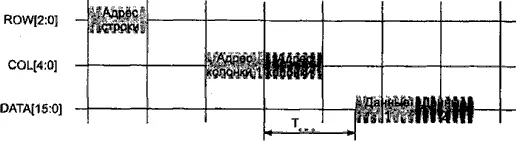

Рис. 7.10. Транзакции записи RDRAM

В микросхемах RDRAM применяется механизм отложенной , или буферированной , записи. Данные для записи (принятый пакет D) сначала помещаются в буфер, из которого несколько позже они выгружаются в усилители считывания-записи (sens amp) по явной команде выгрузки (retire) или автоматически. Буфер записи хранит сами данные, а также номер банка и адрес столбца (но не строки). Буферизация записи позволяет контроллеру посылать команду записи на T RTRраньше, чем этого требует параметр T RCD, что повышает коэффициент использования шины.

Конвейерное выполнение операций RDRAM обеспечивается многобанковой организацией с отдельными усилителями считывания. Пакеты команд по линиям ROW и COL могут идти сплошным потоком, при этом на шине может присутствовать до четырех транзакций. При произвольных обращениях увеличению производительности способствует большое количество банков, практически недостижимое в памяти SDRAM.

Регенерация осуществляется по команде, адресуемой к определенному банку одной или всех микросхем; за период регенерации эта команда должна выдаваться для всех банков.

Память RDRAM отличается высоким энергопотреблением. Средства управления энергопотреблением отключают питание неиспользуемых узлов, однако за 100-кратное снижение мощности в самом экономичном режиме приходится расплачиваться 250-кратным увеличением времени доступа. Микросхемы RDRAM требуют периодической (раз в 100 мс) подстройки выходного тока и термокалибровки; для этих целей имеются специальные команды. Во время подстройки тока микросхемы способны сообщать о своем перегреве.

Вспомогательная шина с сигналами SCK, CMDи SIOслужит для обмена данными с управляющими регистрами и вывода микросхем из состояний пониженного потребления ( PDN и NAP ). Информация по этой шине тоже передается пакетами.

Управляющие регистры хранят информацию об адресе микросхемы, управляют работой микросхемы в различных режимах, содержат счетчики регенерации для банков и строк, параметры настройки временных циклов. В них же можно прочитать информацию о конкретной микросхеме — организация, версия протокола и т. п. В составе управляющих есть и тестовые регистры.

Инициализация памяти включает определение наличия микросхем на шине, назначение им идентификаторов и программирование их параметров. После сброса микросхемы не имеют собственных адресов, а линии SIO0и SIO1у них соединены. В таком состоянии контроллер по шине CMDпосылает широковещательную команду на разъединение линий, после чего для него по линии SIOоказывается доступной только ближайшая микросхема канала. Ей назначается адрес ( SDEVID) и дается команда на соединение линий, в результате к контроллеру подключается вторая микросхема. Она будет пронумерована очередной командой, заставляющей все доступные ненумерованные микросхемы (то есть именно ее) принять указанный номер. Далее замыкаются ее линии SIO, и этот процесс продолжается до самой дальней микросхемы.

После завершения этого «переучета» включается нормальная синхронизация, и дается время для установления режима схем DLL. После двукратной активации и предварительного заряда каждого банка каждой микросхемы память готова к определению доменов синхронизации и назначению каждой микросхеме соответствующих параметров задержек. Также им должны быть присвоены идентификаторы в канале ( DEVID), которые могут и не совпадать со значениями SDEVID(идентификатором на последовательной шине).

Обязательным «фирменным» компонентом ОЗУ на RDRAM является контроллер памяти . В его задачу входит обслуживание микросхем памяти, установленных в канале, по запросам, поступающим со стороны интерфейса системной шины компьютера. Часть контроллера, обращенная к каналу, инвариантна к архитектуре компьютера. Именно она «знает» протокол RDRAM и является продуктом фирмы Rambus. Контроллер RDRAM встраивается в чипсеты для процессоров P6 (например, 1820, 1840), Pentium 4 (1850 с 32-разрядным каналом, то есть уже под пары модулей RIMM) и других архитектурных линий.

В соответствии со спецификацией RDRAM в одном канале может быть до трех слотов под RIMM, и их интерфейсные линии соединяются змейкой. В слоты могут устанавливаться RIMM различной емкости (сейчас они выпускаются на 64, 96, 128 и 256 Мбайт). Однако пока что фирме Intel не удалось достичь устойчивой работы канала с тремя модулями и пришлось ограничиться двумя. Теперь в памяти появился новый элемент-пустышка Continuity module . Это как бы модуль RIMM, но без микросхем памяти, и нужен он для того, чтобы замыкать цепь канала Rambus. Такая «заглушка» должна устанавливаться во все слоты канала, не занятые под модули RIMM. Если используются не все слоты, то память выгоднее ставить ближе к контроллеру — она будет работать быстрее (см. выше).

7.1.4. Память с виртуальными каналами — VC DRAM

Идея архитектуры памяти с виртуальными каналами (VirtualChannel Memory Architecture, не путать с виртуальной памятью!) заключается в помещении между массивом запоминающих ячеек и внешним интерфейсом микросхемы памяти набора канальных буферов . При этом операции обмена данными разделяются на два процесса: «фасадный» обмен данными с каналами и «тыловой» обмен между каналами и массивом запоминающих ячеек. Оба процесса выполняются по командам со стороны внешнего интерфейса почти независимо друг от друга. Архитектура виртуальных каналов приложима к памяти любого типа, включая ПЗУ и флэш-память, но наиболее интересна она в приложении к динамической памяти — VC DRAM.

Устройство VC DRAM рассмотрим на примере микросхем емкостью 128 Мбит, на которых строятся выпускаемые модули DIMM VC DRAM. По интерфейсу (составу и уровням сигналов) микросхемы и модули VC DRAM аналогичны обычным микросхемам SDRAM, но отличаются системой команд. Микросхемы имеют такую же внешнюю организацию по 4,8 или 16 бит данных, но совершенно иную внутреннюю архитектуру. Они имеют две матрицы (два банка) запоминающих ячеек размером 8 К×8 К, то есть каждая строка имеет объем 8 Кбит и состоит из четырех сегментов размером по 2 Кбит. Между матрицами и внешним интерфейсом имеется 16 канальных буферов , каждый объемом 2 Кбит. За одно обращение к матрице выполняется параллельная передача 2 Кбит данных между одним из буферов и сегментом выбранной строки. Это «тыловой» обмен реализуют команды PRF(Prefetch — чтение массива в буфер) и RST(Restore — сохранение буфера в массиве), в которых микросхеме указывается номер банка, номер сегмента и номер канала. Предварительно командой ACTдолжна быть активирована требуемая строка матрицы (при подаче этой команды задается банк и адрес строки). Деактивация строк (предварительный заряд) может быть автоматической, сразу после выполнения обращений к массиву (для этого имеются специальные команды предвыборки и сохранения — PRFAи RSTA) или же по специальным командам, деактивирующим выбранный банк или оба банка сразу.

Интервал:

Закладка:

![Михаил Барятинский - Танки III Рейха. Том III [Самая полная энциклопедия]](/books/1094087/mihail-baryatinskij-tanki-iii-rejha-tom-iii-samaya.webp)