Стивен Барретт - Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С

- Название:Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С

- Автор:

- Жанр:

- Издательство:Издательский дом «ДМК-пресс»

- Год:2007

- Город:Москва

- ISBN:5-9706-0034-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Стивен Барретт - Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С краткое содержание

В книге последовательно рассматриваются все этапы создания встраиваемых систем на микроконтроллерах с применением современных технологий проектирования. Задумав эту книгу, авторы поставили перед собой задачу научить читателя искусству создания реальных устройств управления на однокристальных микроконтроллерах.

Издание содержит материал, охватывающий все вопросы проектирования, включает множество заданий для самостоятельной работы, примеры программирования, примеры аппаратных решений и эксперименты по исследованию работы различных подсистем микроконтроллеров.

Данная книга является прекрасным учебным пособием для студентов старших курсов технических университетов, которые предполагают связать свою профессиональную деятельность с проектированием и внедрением встраиваемых микропроцессорных систем. Книга также будет полезна разработчикам радиоэлектронной аппаратуры на микроконтроллерах.

Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12/HCS12 с применением языка С - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Для центрированной ШИМ (CENTR = 1) расчет временных параметров выходного сигнала следует производить по формулам:

• Период ШИМ–сигнала равен

T PWM= 2 × (PWPERx + 1)/fx

• Длительность импульса с высоким активным уровнем при PPOLx = 1 равна

T IMP= 2 × (PWDTYx + 1) / [(PWPERx + 1) × fx]

Коэффициент заполнения в этом же режиме равен

γ = (PWPERx – PWDTYx)/[(PWPERx + 1) × fx] × 100%

• Длительность импульса с высоким активным уровнем при PPOLx = 0 равна

T IMP= 2 × (PWPERx – PWDTYx) / [(PWPERx + 1) × fx]

Коэффициент заполнения в этом же режиме равен

γ = [(PWDTYx + 1)/(PWPERx + 1)] × 100%,

Обратите внимание, что при одинаковой частоте тактирования и одинаковых кодах в регистрах периода и коэффициента заполнения длительность импульса и период формируемого сигнала центрированной ШИМ будет в два раза больше, чем при фронтовой ШИМ. А коэффициент заполнения при этом остается одинаковым, поскольку является величиной относительной.

4.24.3. Система тактирования

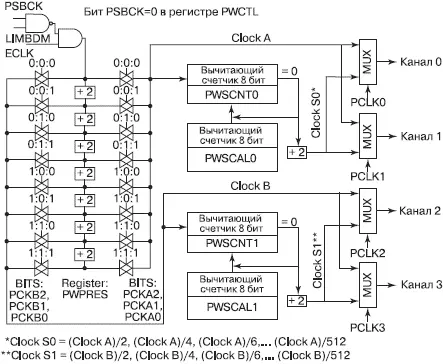

Структурная схема системы тактирования модуля PWM представлена на рис. 4.100. Первичным генератором для тактирования счетчиков каналов модуля PWM служит импульсная последовательность E_CLOСK. На выходе программируемого делителя формируются две импульсные последовательности CLOСK_A и CLOСK_B. Причем сигнал CLOСK_A используется для тактирования каналов 0 и 1, а CLOСK_B — каналов 2 и 3. Коэффициенты деления для последовательностей CLOСK_A и CLOСK_B задаются битами PCKA[2:0] и PCKB[2:0] регистра конфигурации PWCLK. Возможные значения коэффициентов деления приведены в таблице рис. 4.101.

Рис. 4.100.Структурная схема системы тактирования модуля PWM

| PCKA2 (PCKB2) | PCKA1 (PCKB1) | PCKA0 (PCKB0) | Частота CLOСK_A, CLOСK_B |

|---|---|---|---|

| 0 | 0 | 0 | E |

| 0 | 0 | 1 | E + 2 |

| 0 | 1 | 0 | E + 4 |

| 0 | 1 | 1 | E + 8 |

| 1 | 0 | 0 | E + 16 |

| 1 | 0 | 1 | E + 32 |

| 1 | 1 | 0 | E + 64 |

| 1 | 1 | 1 | E + 128 |

Рис. 4.101.Выбор частоты тактирования счетчиков каналов модуля PWM

При необходимости коэффициент деления может быть увеличен посредством подключения дополнительного делителя на входе каждой пары каналов. Делитель 0 обслуживает каналы 0 и 1 (рис. 4.100), он формирует свой выходной сигнал из импульсной последовательности CLOСK_A. Делитель 1 обслуживает каналы 2 и 3 (рис. 4.100) и формирует выходной сигнал из последовательности CLOСK_B. Коэффициент деления каждого из этих делителей определяет код в регистрах PWSCAL0 и PWSCAL1.

4.24.4. Регистры модуля PWM

Множество регистров специальных функций, которые обслуживают модуль PWM, можно разделить на следующие группы:

• Регистры конфигурации;

• Регистр разрешения работы каналов;

• Регистр дополнительного делителя;

• Регистры делителей 0 и 1;

• Регистры счетчика каналов;

• Регистры периода каналов;

• Регистры коэффициента заполнения каналов;

• Регистр управления;

• Регистр специальных режимов модуля;

• Регистры работы с портом P.

Рассмотрим перечисленные регистры более подробно.

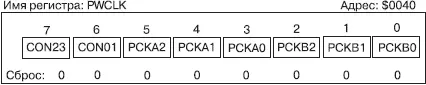

Регистр конфигурации PWCLK выполняет две функции. Во-первых, его биты определяют, будут ли каналы модуля использоваться в 8-разрядном режиме, или эти каналы объединят попарно для работы в 16-разрядном режиме. Во-вторых, биты регистра назначают два коэффициента деления частоты для образования из импульсной последовательности E_CLOСK сигнала тактирования каналов 0 и 1 (CLOСK_A) и сигнала тактирования каналов 2 и 3 (CLOСK_B).

Формат регистра PWCLK представлен на рис. 4.102. Биты CON23 и CON01 определяют режимы работы пар каналов 2:3 и 0:1 соответственно. Если значение бита CON23 равно 0, то каналы 2 и 3 работают независимо друг от друга с 8-разрядным разрешением. При CON23 = 1 каналы 2 и 3 объединяются в один 16-разрядный генератор ШИМ-сигнала. Действие бита CON01 по отношению к каналам 0 и 1 аналогично.

Рис. 4.102.Формат регистра конфигурации PWCLK

Если каналы объединены в пару, то ШИМ-сигнал пары 0:1 формируется на линии 0 порта PORT P, пары 2:3 — на линии 2 порта PORT P. Однако управление полярностью выходных сигналов 16-разрядных ШИМ-генераторов осуществляется битами PPOL1 для пары 0:1 и PPOL3 для пары 2:3. Биты управления полярностью PPOLx располагаются в регистре PWPOL.

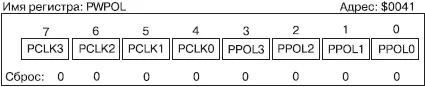

Регистр конфигурации PWPOL предназначен для задания активного уровня выходного сигнала каждого из четырех ШИМ-генераторов, а также для разрешения включения дополнительного делителя частоты для сигналов тактирования CLOСK_A и CLOСK_B. Формат регистра PWPOL приведен на рис. 4.103.

Рис. 4.103.Формат регистра конфигурации PWPOL

Каждому каналу поставлен в соответствие бит полярности сигнала PPOLx и бит выбора источника тактирования канала PCLKx (x — номер канала). Если бит PPOLx=1, то активный уровень ШИМ-сигнала — высокий логический (рис. 4.98). При PPOLx = 0 на выходе канала формируется ШИМ-сигнал с низким логическим уровнем на интервале γT (рис. 4.98).

Если бит PCLKx равен 0, то для соответствующего канала в качестве источника тактирования назначается импульсная последовательность CLOСK_A (каналы 0 и 1) или CLOСK_B (каналы 2 и 3). При PCLKx = 0 соответствующий канал тактируется от дополнительного делителя частоты, который конфигурируется битами регистров PWSCNT0/PWSCNT1 и PWSCAL0/PWSCAL1.

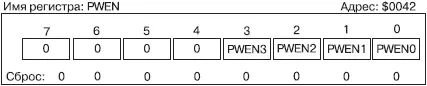

Отдельные биты регистра конфигурации PWEN используются для активизации каналов модуля PWM. Формат регистра PWEN представлен на рис. 4.104. Если бит PWENx установлен в 1, то канал с номером «x» генерирует импульсную последовательность на соответствующем выводе порта PORT P. При PWENx = 0 канал находится в неактивном режиме, соответствующая линия порта PORT P может использоваться как линия ввода/вывода общего назначения.

Рис. 4.104.Формат регистра разрешения работы каналов PWEN

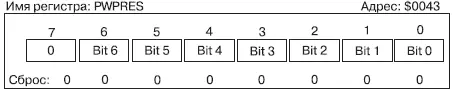

Этот регистр используется только в специальных режимах работы МК. Его формат представлен на рис. 4.105. Более подробно мы не будем его рассматривать.

Рис. 4.105.Формат регистра дополнительного делителя PWPRES

Прежде, чем приступить к рассмотрению двух следующих регистров, возвратимся к рис. 4.100 и вспомним, как организована система тактирования отдельных каналов модуля PWM. Источником тактирования каналов является импульсная последовательность E_CLOСK. Два программируемых делителя образуют из E_CLOСK сигналы тактирования CLOСK_A для каналов 0 и 1 и CLOСK_B для каналов 2 и 3. Причем каждый из каналов может тактироваться от указанного сигнала или напрямую, или через дополнительный делитель. Регистры PWSCNT0/PWSCNT1 и PWSCAL0/PWSCAL1 устанавливают режимы работы этих двух дополнительных делителей.

Читать дальшеИнтервал:

Закладка: