Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Рассмотрим подробнее механизм автоматической загрузки сигнального процессора из ПЗУ, для лучшего понимания происходящих при этом процессов. При подаче питания на тестовую плату, описанную в гл. 3, цепь сброса R1, CP1 формирует сигнал -RKEY, который устанавливает триггер, построенный на элементах D6.1 и D6.2, в состояние, при котором сигнал BMODE будет находиться в состоянии логического нуля. Сигнальный процессор анализирует состояние данного сигнала и сигнала на входе вывода MMAP после сброса и распознает, что загрузка программы в программную память процессора будет производиться из ПЗУ через интерфейс BDMA. При этом процессор автоматически заносит в регистры порта BDMA определенные значения, описанные в предыдущей главе, для того чтобы произвелась автоматическая загрузка 32 слов программы-загрузчика разрядностью 24 бита побайтно в программную память процессора и затем ей было передано управление для загрузки остальной части программы.

Как было сказано выше, программа-загрузчик автоматически записывается в начало файла прошивки ПЗУ с помощью сплиттера во время трансляции программы. После автоматической загрузки из ПЗУ в память программ процессора 32 слов программы- загрузчика через интерфейс BDMA происходит перезапуск процессора и начинает выполняться программа загрузчика, которая осуществляет полную загрузку основной рабочей программы из ПЗУ в процессор.

После чего вновь происходит перезапуск процессора, и начинает выполняться основная загруженная программа. При загрузке основной программы загрузчик полностью замещается в программной памяти процессора самой программой. Такой непростой механизм загрузки реализован разработчиками процессора с целью обеспечения гибкости при загрузке процессора, и для обеспечения возможности разработчикам программного обеспечения создавать собственные загрузчики программ. Машинные коды загрузчика можно увидеть в первых байтах файла mem_clr.bin с помощью любого редактора шестнадцатеричных файлов или простой программы просмотра файлов.

В файле mem_clr.bin и в ПЗУ все коды 24-разрядных слов команд процессора располагаются в строгом порядке. Первым располагается в ПЗУ старший байт команды, затем следует средний байт и последним записывается младший байт команды. Формат хранения слов программы в ПЗУ приведен в табл. 7.1.

Таблица 7.1 Формат хранения слов программы в ПЗУ

| Адрес памяти программ | Слово программы | Адрес памяти ПЗУ | Байты программы |

|---|---|---|---|

| 0x0000 | 0xABCDEF | 0x00 | 0xAB |

| 0x01 | 0xCD | ||

| 0x02 | 0xEF | ||

| 0x0001 | 0x123456 | 0x03 | 0x12 |

| 0x04 | 0x34 | ||

| 0x05 | 0x56 | ||

| и т.д. |

Способ загрузки процессора из ПЗУ хорошо применим для автономных процессорных устройств, работающих под управлением одной программы. Однако на практике довольно часто встречаются задачи, когда необходимо оперативно менять управляющую программу для процессора какого-либо электронного устройства. Это также необходимо при отладке программ с многочисленными итерациями трансляции и загрузки отлаживаемой программы в процессор. Удачным решением для такого рода задач является загрузка программ в сигнальный процессор через интерфейсный порт процессора IDMA. Но прежде чем начать освоение данной процедуры, необходимо подробнее познакомиться с этим интерфейсом. С этого мы продолжим изучение сигнального процессора в следующей главе.

Глава 8. Порт IDMA

В этой главе описывается интерфейсный порт IDMA и способы загрузки и отладки программ для сигнального процессора через этот порт.

Помимо порта прямого доступа к байтовой памяти BDMA (Byte Data Memory Access), сигнальный процессор ADSP-2181 имеет порт прямого доступа к внутренней памяти процессора IDMA (Internal Data Memory Access). Он представляет собой 16-разрядный параллельный порт, через который можно читать и записывать данные памяти процессора. Порт IDMA имеет 16-разрядную мультиплексированную шину адреса/данных IAD0–IAD15, 4 сигнала управления и 1 сигнал контроля. К сигналам управления относятся: сигнал выбора порта -IS, сигнал записи адреса ячейки памяти IAL, сигнал чтения -IRD и записи -IWR данных через порт. Сигнал контроля -IACK позволяет определить готовность порта IDMA. При чтении и записи памяти через IDMA данные транслируются через буферный регистр порта IDMA. В памяти данных процессора по адресу 0x3FE0 находится регистр управления IDMA, который предназначен для хранения адреса ячейки памяти, к которой будет производиться обращение через порт IDMA. Формат этого регистра представлен в табл. 8.1.

Таблица 8.1 Формат данных регистра управления IDMA

| Разряд | Назначение |

|---|---|

| 15 | Не используется |

| 14 | Указатель типа памяти: 0=память программ (РМ) 1=память данных (DM) |

| 13–0 | Значение начального адреса памяти процессора при обмене через IDMA (от 0 до 0x3FFF) |

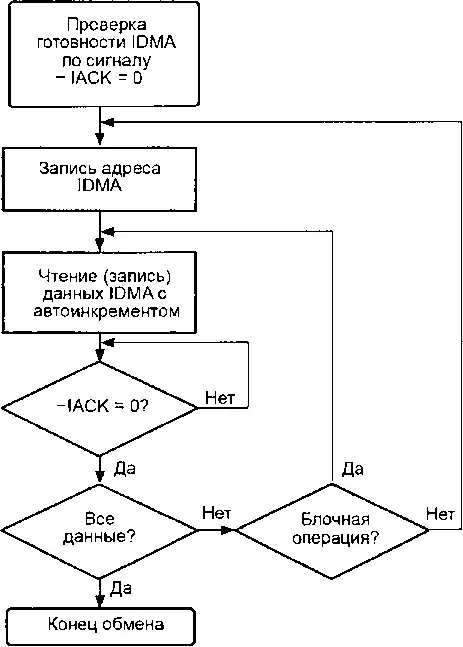

Порт IDMA имеет встроенную функцию автоинкремента (автоматического увеличения на единицу адреса памяти), что позволяет ускорить выполнение блочных операций. Кроме того, порт IDMA позволяет выполнять загрузку памяти программ процессора с автоматическим запуском программы после заполнения нулевой ячейки памяти. Протокол обращения к памяти процессора через порт IDMA достаточно прост и показан на рис. 8.1.

Рис. 8.1. Алгоритм обращения к памяти процессора

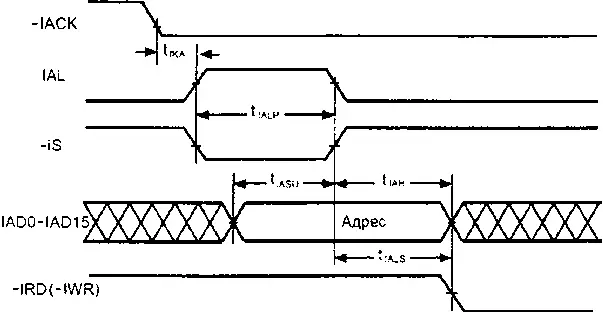

Вначале все сигналы управления портом переводятся в пассивное состояние и проверятся готовность IDMA, путем ожидания установки сигнала -IACK в логический ноль. Затем осуществляется вывод на шину IAD0–15 сигналов адреса памяти процессора, к которой будет производиться обращение. После чего формируется строб сигнала записи адреса IAL в регистр управления порта IDMA. Временная диаграмма данной операции показана на рис. 8.2, а в табл. 8.2 приведены временные параметры для этой диаграммы.

Рис. 8.2. Временная диаграмма операции защелкивания адреса IDMA

Таблица 8.2 Временные параметры диаграммы защелкивания адреса IDMA

| Параметр | Минимум |

|---|---|

| Защелкивание адреса IDMA | |

| Требуемые длительности: | |

| t IALPдлительность защелкивания адреса, нс 1,2 | 10 |

| t IASUустановка адреса перед окончанием защелкивания, нс 2 | 5 |

| t IAHудержание адреса после защелкивания, нс 2 | 2 |

| t IKA-IACK=0 перед защелкиванием, нс 1 | 0 |

| t IALSначало записи или чтения после защелкивания, нс 2,3 | 3 |

Примечания:

1 Начало защелкивания — IS=0 и IAL=1.

Читать дальшеИнтервал:

Закладка: