Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

В свою очередь, фирма Motorola выпустила сигнальные процессоры семейства DSP56000, которые имеют разрядность 24 бита, двойную внутреннюю шину данных X и Y, удобную при операциях с комплексными числами, и обладают высокой степенью конвейеризации и параллелизма. Эти свойства делают данные процессоры еще более производительными и удобными для цифровой обработки сигналов.

Еще один производитель в лице фирмы AT&T Microelectronics выпускает сигнальные процессоры серии DSP16, которые отличаются наличием кэш-памяти и встроенного высокоскоростного, до 30 Мбайт, параллельного порта.

Фирма Analog Devices вышла на рынок сигнальных процессоров со своей серией ADSP-21XX, которые конкурируют с выше рассмотренными моделями по некоторым техническим параметрам, а кроме того, по цене. Например, процессор ADSP-21msp50 имеет встроенные АЦП и ЦАП и в то же время его стоимость составляет несколько долларов.

На этом развитие сигнальных процессоров не остановилось, и уже в конце 1980-х годов на рынке появились процессоры третьего поколения от перечисленных выше фирм. Отличительной особенностью этого поколения стало появление двоичной плавающей арифметики, увеличение разрядности шины данных, емкости памяти и программ. К этому числу процессоров можно отнести TMS320C30 фирмы Texas Instruments, DSP96002 фирмы Motorola, DSP32C фирмы AT&T Microelectronics и ADSP21020 фирмы Analog Devices.

Впоследствии на рынке появились сигнальные процессоры других фирм. Однако в настоящее время, лидирующее положение в этой области занимают фирмы Texas Instruments, Motorola, AT&T Microelectronics и Analog Devices.

История развития сигнальных процессоров на этом не заканчивается, и можно было бы продолжать ее повествование, но целью данной книги является не исторический рассказ, а практическое руководство по освоению и приобретению навыков работы с этими перспективными компонентами. Поэтому я хочу остановиться на более подробном описании внутренней архитектуры и практического применения одного из сигнальных процессоров фирмы Analog Devices. Именно об этом и пойдет речь в следующей главе.

Глава 2. Архитектура

В этой главе описывается внутренняя архитектура одного из сигнальных процессоров фирмы Analog Devices ADSP-2181 и примеры его подключения.

Фирма Analog Devices разработала целые семейства сигнальных процессоров и постоянно продолжает выпускать на рынок новые модели. В настоящее время существуют следующие семейства: ADSP-21XX, Shark DSP, BlackFin DSP и др. Но, несмотря на все многообразие этих групп, все они имеют похожую друг на друга архитектуру. Отличие семейств друг от друга заключается, например, в арифметических блоках, которые поддерживают вычисления с фиксированной или плавающей запятой. Кроме того, семейства отличаются производительностью, разрядностью шин данных, структурой внутренних регистров, интерфейсами и т.п. Отличие процессоров друг от друга внутри семейства состоит в основном в объеме и организации внутренней памяти и типе встроенных интерфейсов. В состав каждого из процессоров этого семейства входят следующие функциональные устройства.

• Арифметико-логическое устройство АЛУ.

• Умножитель-накопитель.

• Устройство сдвига.

• Два генератора адреса данных.

• Программный автомат.

• Таймер.

• Последовательный многоканальный порт.

Ниже приведена табл. 2.1 с отличительными характеристиками сигнальных процессоров семейства ADSP-21XX.

Таблица 2.1. Характеристики сигнальных процессоров семейства ADSP-21XX

| Ресурсы | 2101 | 2103 | 2105 | 2111 | 2115 | 21msp58 | 2171 | 2173 | 2181 | 2183 |

|---|---|---|---|---|---|---|---|---|---|---|

| Объем оперативной памяти программ (слов) | 2K | 2K | 1K | 2K | 1K | 2K | 2K | 2K | 16K | 16K |

| Объем оперативной памяти данных (слов) | 1K | 1K | 512 | 1K | 512 | 2K | 2K | 2K | 16K | 16K |

| Второй последовательный порт | - | - | - | - | - | - | - | - | + | + |

| Порт хост-интерфейса | - | - | - | + | - | + | + | + | - | - |

| Порт прямого доступа к памяти | - | - | - | - | - | - | - | - | + | + |

| Максимальная внешняя тактовая частота, МГц | 20 | 10,24 | 13,82 | 20 | 20 | 16,67 | 16,67 | 16,67 | 20 | 20 |

| Аналого-цифровые преобразователи и фильтры | - | - | - | - | - | + | - | - | - | - |

| Режим малого потребления | - | - | - | - | - | + | + | + | + | + |

| Напряжение питания, В | 5 | 3,3 | 5 | 5 | 5 | 5 | 5 | 3,3 | 5 | 3,3 |

| Количество сигнальных выводов | 68 | 68 | 68 | 100 | 68 | 100 | 128 | 128 | 128 | 128 |

Остановимся на рассмотрении архитектуры одного из самых распространенных на сегодняшний день процессоров семейства ADSP-21XX, а именно на процессоре ADSP-2181. Этот компонент является самым развитым в своем семействе и включает в себя наибольший объем памяти и множество встроенных интерфейсов.

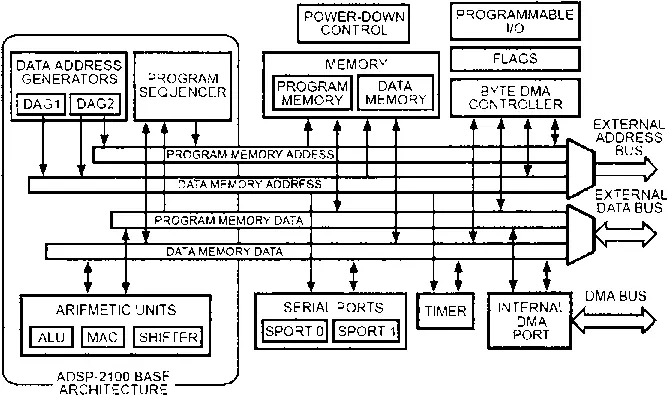

Сигнальный процессор ADSP-2181 представляет собой однокристальный чип, выпускаемый в 128 выводных корпусах типа PQFP-128 или TQFP-128. Из вышеприведенной информации уже можно составить общее представление о возможностях, заложенных в данный процессор. Но для полноты картины рассмотрим структурную схему внутренней архитектуры этого чипа, приведенную на рис. 2.1.

Рис. 2.1. Структурная схема внутренней архитектуры чипа

Процессор имеет сильно развитую структуру внутренних шин адреса и данных. К их числу относятся шина адреса памяти программ PROGRAM MEMORY ADDRESS, шина адреса памяти данных DATA MEMORY ADDRESS, шина данных памяти программ PROGRAM MEMORY DATA и шина данных памяти данных DATA MEMORY DATA.

Слева на схеме изображен базовый блок архитектуры всего семейства ADSP-2100 BASE ARCHITECTURE включаемый в состав любого из процессоров данного семейства. Он состоит из блока генераторов адреса данных DATA ADDRESS GENERATORS, программного автомата PROGRAM SEQUENCER и арифметического блока ARITHMETIC UNITS.

Блок генераторов адреса данных содержит два генератора: DAG1 и DAG2, предназначенных для инвертирования бит адреса во время выполнения процессором операций быстрого преобразования Фурье (БПФ).

Программный автомат осуществляет поддержку операций с условными переходами, вызов подпрограмм и возврат в основную программу, ускоряя тем самым работу процессора в целом.

Арифметический блок включает в себя арифметико-логическое устройство ALU, умножитель с накопителем MAC и устройство сдвига SHIFTER. Первый из этих блоков предназначен для выполнения арифметических и логических операций над данными, а второй для выполнения арифметического умножения чисел. SHIFTER позволяет нормировать числа после выполнения арифметических операций.

Читать дальшеИнтервал:

Закладка: