Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Внутри процессора производится аппаратное умножение внешней частоты, которая затем используется для синхронизации процессора. Внутренняя частота процессора будет составлять 40 МГц, а длительность выполнения команд 25 нс. Внутренняя частота выводится также на CLKOUT процессора и может быть использована для синхронизации других микросхем, подключаемых к процессору.

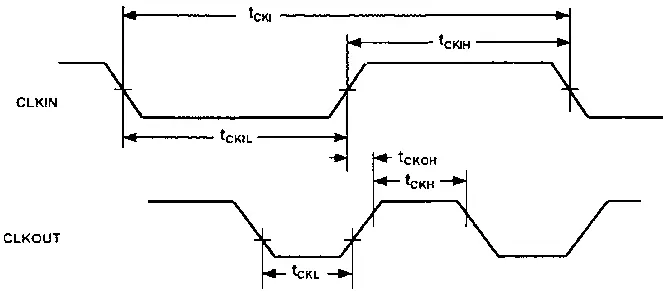

Временная диаграмма сигналов синхронизации показана на рис. 3.2, а допустимые параметры этих сигналов приведены в табл. 3.1.

Рис. 3.2. Временная диаграмма сигналов синхронизации

Таблица 3.1 Допустимые параметры сигналов синхронизации процессора

| Параметр | Минимум | Максимум | Единица измерения |

|---|---|---|---|

| Сигналы синхронизации | |||

| Требуемые длительности: | |||

| t CKI | 50 | 150 | нс |

| t CKIL | 20 | нс | |

| t CKIH | 20 | нс | |

| Характеристика переключения: | |||

| t CKL | 0,5t CK-7 | нс | |

| t CKH | 0,5t CK-7 | нс | |

| t CKOH | 0 | 20 | нс |

t CK= 0,5*t CKI

При выборе сигнального процессора необходимо пользоваться табл. 3.2, в которой приведены заводские маркировки и соответствующие им характеристики.

Таблица 3.2 Характеристики сигнальных процессоров

| Заводская маркировка | Рабочий температурный диапазон, °С | Максимальная тактовая частота, МГц | Тип корпуса | Условное обозначение корпуса |

|---|---|---|---|---|

| ADSP-2181KST-115 | 0…+70 | 28,8 | TQFP-128* | ST-128 |

| ADSP-2181BST-115 | -40…+85 | 28,8 | TQFP-128 | ST-128 |

| ADSP-2181KS-115 | 0…+70 | 28,8 | PQFP-128** | S-128 |

| ADSP-2181BS-115 | -40…+85 | 28,8 | PQFP-128 | S-128 |

| ADSP-2181KST-133 | 0…+70 | 33,3 | TQFP-128 | ST-128 |

| ADSP-2181BST-133 | -40…+85 | 33,3 | TQFP-128 | ST-128 |

| ADSP-2181KS-133 | 0…+70 | 33,3 | PQFP-128 | S-128 |

| ADSP-2181BS-133 | -40…+85 | 33,3 | PQFP-128 | S-128 |

| ADSP-2181KST-160 | 0…+70 | 40 | TQFP-128 | ST-128 |

| ADSP-2181 KS-160 | 0…+70 | 40 | PQFP-128 | S-128 |

* TQFP — Plastic Thin Quad Flatpack (пластиковый тонкий четырехугольный плоский корпус).

** PQFP — Plastic Quad Flatpack (пластиковый четырехугольный плоский корпус).

В нашем случае использован процессор ADSP-2181KS-133 в корпусе PQFP-128, как получивший большое распространение и легко доступный. В табл. 3.3 приведено соответствие выводов корпуса этого процессора его сигналам.

Таблица 3.3 Соответствие выводов корпуса сигналам процессора

| Вывод | Сигнал | Вывод | Сигнал | Вывод | Сигнал | Вывод | Сигнал |

|---|---|---|---|---|---|---|---|

| 1 | PF0 | 33 | PWD | 65 | EBR | 97 | D23 |

| 2 | WR | 34 | IRQ2 | 66 | BR | 98 | GND |

| 3 | RD | 35 | BMODE | 67 | EBG | 99 | IWR |

| 4 | IOMS | 36 | PWDACK | 68 | BG | 100 | IRD |

| 5 | BMS | 37 | IACK | 69 | VDD | 101 | IAD15 |

| 6 | DMS | 38 | BGH | 70 | DO | 102 | IAD14 |

| 7 | CMS | 39 | VDD | 71 | D1 | 103 | IAD13 |

| 8 | GND | 40 | GND | 72 | D2 | 104 | IAD12 |

| 9 | VDD | 41 | IRQL0 | 73 | D3 | 105 | IAD11 |

| 10 | PMS | 42 | IRQL1 | 74 | D4 | 106 | IAD10 |

| 11 | А0 | 43 | FLO | 75 | GND | 107 | IAD9 |

| 12 | A1 | 44 | FL1 | 76 | D5 | 108 | IAD8 |

| 13 | A2 | 45 | FL2 | 77 | D6 | 109 | IAD7 |

| 14 | A3 | 46 | DT0 | 78 | D7 | 110 | IAD6 |

| 15 | A4 | 47 | TFS0 | 79 | D8 | 111 | VDD |

| 16 | A5 | 48 | RFS0 | 80 | D9 | 112 | GND |

| 17 | A6 | 49 | DR0 | 81 | D10 | 113 | IAD5 |

| 18 | A7 | 50 | SCLK0 | 82 | D11 | 114 | IAD4 |

| 19 | XTAL | 51 | DT1/FO | 83 | D12 | 115 | IAD3 |

| 20 | CLKIN | 52 | TFS1/IRQ1 | 84 | D13 | 116 | IAD2 |

| 21 | GND | 53 | RFS1/IRQ0 | 85 | D14 | 117 | IAD1 |

| 22 | CLKOUT | 54 | GND | 86 | GND | 118 | IAD0 |

| 23 | GND | 55 | DR1/FI | 87 | VDD | 119 | PF7 |

| 24 | VDD | 56 | SCLK1 | 88 | GND | 120 | PF6 |

| 25 | A8 | 57 | ERESET | 89 | D15 | 121 | PF5 |

| 26 | A9 | 58 | RESET | 90 | D16 | 122 | PF4 |

| 27 | A10 | 59 | EMS | 91 | D17 | 123 | GND |

| 28 | A11 | 60 | ЕЕ | 92 | D18 | 124 | IS |

| 29 | A12 | 61 | ECLK | 93 | D19 | 125 | IAL |

| 30 | А13 | 62 | ELOUT | 94 | D20 | 126 | PF3 |

| 31 | IRQE | 63 | ELIN | 95 | D21 | 127 | PF2 |

| 32 | MMAP | 64 | EINT | 96 | D22 | 128 | PF1 |

Сигнал -RESET обеспечивает сброс процессора в исходное состояние. Этот сигнал должен находиться в активном низкоуровневом состоянии при включении и перезагрузке процессора в течение не менее пяти тактовых периодов внешней синхронизации процессора. Обычно для надежного сброса процессора этот сигнал удерживается в активном состоянии не менее нескольких микросекунд. Формирование сигнала сброса в схеме возможно от любого из двух источников. Первый источник этого сигнала реализован на зарядной цепочке R1, CP1. В момент подачи питания на схему, конденсатор CP1 разряжен и на нем удерживается низкий потенциал в течении времени его заряда, достаточного для приведения процессора в исходное состояние. Диод VD1 обеспечивает быстрый разряд этого конденсатора в момент отключения или кратковременного пропадания питания. Кнопка SB4 предназначена для принудительного сброса процессора вручную. Резистор R2 ограничивает ток разряда, предохраняя контакты кнопки от образования искр, и устраняет дребезг контактов совместно с конденсатором CP1. Вторым источником сигнала сброса является сигнал — RESI с разъема XU1, который буферизуется шинным повторителем D4.1 и поступает на микросхему D6. С помощью элементов D6.3 и D6.4 оба сигнала объединяются в один сигнал сброса процессора в инверсном (-RESET) и неинверсном виде (RESET). Наличие неинверсного сигнала требуется для сброса других микросхем с активным высокоуровневым входом сброса.

Сигнал -ERESET и сигналы на выводах 59…65 и 67 процессора предназначены для подключения к нему специального аппаратного эмулятора EZ-ICE, который можно приобрести через представителей фирмы Analog Device в России. Выводы эмулятора подключены к разъему XEZ в соответствии с рекомендациями по применению данного сигнального процессора. Однако на практике вполне можно обходиться и без этого эмулятора.

Следующая группа сигналов -IRQL0, -IRQL1, -IRQ2 и -IRQE отвечает за передачу процессору внешних прерываний. В качестве источников прерываний могут выступать различные микросхемы, датчики, кнопки и т.п. Так, к сигнальному выводу -IRQE подключена кнопка SB5 через цепочку устранения дребезга контактов R22 и CP4. Резистор R23 предназначен для удержания сигнала прерывания в пассивном состоянии. В дальнейшем с ее помощью можно будет принудительно вызывать прерывание процессора при необходимости.

Читать дальшеИнтервал:

Закладка: