Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

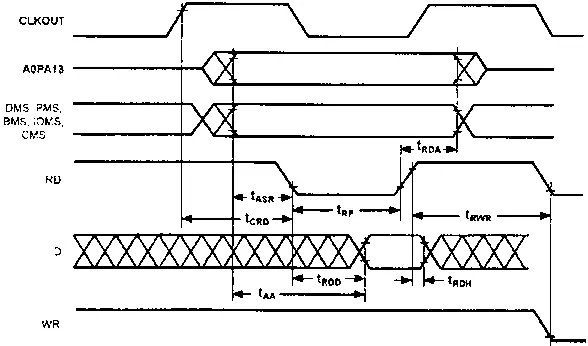

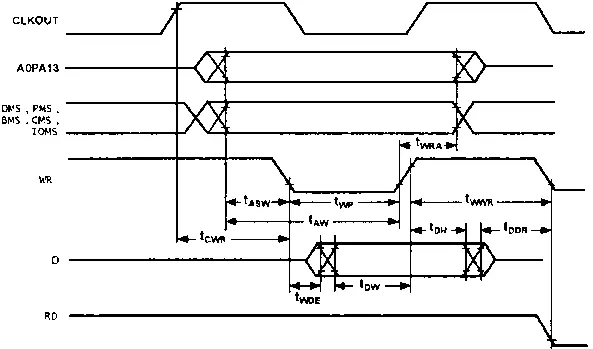

Временные диаграммы циклов чтения и записи данных процессором, представлены на рис. 3.3 и 3.4, соответственно. Параметры сигналов для этих циклов приводятся в табл. 3.4 и 3.5.

Рис. 3.3. Временная диаграмма цикла чтения

Рис. 3.4. Временная диаграмма цикла записи

Таблица 3.4 Параметры сигналов для цикла чтения данных процессором

| Параметр | Минимум | Максимум | Единица измерения |

|---|---|---|---|

| Чтение памяти | |||

| Требуемые длительности: | |||

| t RDD | 0,5 t CK- 9 + w | нс | |

| t AA | 0,25 t CK- 10.5 + w | нс | |

| t RDH | 0 | нс | |

| Характеристика переключения: | |||

| t RP | 0,5 t CK- 5 + w | 0,25 t CK+ 7 | нс |

| t CRD | 0,25 t CK- 5 | нс | |

| t ASR | 0,25 t CK- 6 | нс | |

| t RDA | 0,25 t СK- 3 | нс | |

| t RWR | 0,5 t CK- 5 | нс |

Таблица 3.5 Параметры сигналов для цикла записи данных процессором

| Параметр | Минимум | Максимум | Единица измерения |

|---|---|---|---|

| Запись памяти | |||

| Характеристика переключения: | |||

| t DW | 0,5 t СK- 7 + w | нс | |

| t DH | 0,25 t СK- 2 | нс | |

| t WP | 0,5 t CK- 5 + w | нс | |

| t WDE | 0 | нс | |

| t ASW | 0,25 t CK- 6 | нс | |

| t DDR | 0,25 t CK- 7 | нс | |

| t CWR | 0,25 t CK- 5 | нс | |

| t AW | 0,75 t CK- 9 + w | 0,25 t СK+ 7 | нс |

| t WRA | 0,25 t CK- 3 | нс | |

| t WWR | 0,5 t CK- 5 | нс |

* w — число циклов задержки * t CK

Из приведенных данных видно, что чтение и запись данных в процессор необходимо производить по нарастающему фронту сигналов чтения или записи соответственно, когда обеспечена достоверность данных на шине.

Следующая группа сигналов FL0-FL2 является битовыми выходными сигналами, которые работают только на вывод. К ним подключены индикаторы HL0-HL2 через буферный повторитель D4.2.

В отличие от FL0-FL2, выводы PF0-PF7 являются двунаправленными битовыми сигналами и могут быть запрограммированы как на ввод, так и на вывод побитно. Так, к выводу PF7 подключен индикатор HL3, а выводы PF0-PF3 будут запрограммированы как входы и к ним подключены кнопки SB0-SB3. Резисторы R5–R8 являются токоограничивающими, а резисторная сборка RN3 подтягивает сигналы управления и входные сигналы к высокому уровню.

Назначение сигнала MMAP было показано в предыдущей главе при рассмотрении способов организации памяти процессора. Поскольку в нашей схеме используется внутренняя память процессора и задействован механизм загрузки процессора, этот вывод подключен к нулевому потенциалу.

Сигнал -PWD отвечает за формирование немаскируемого прерывания при снижении питания процессора ниже нормы. Для его использования необходимо подключить к нему выход узла, отслеживающего напряжение питания и формирующего потенциал низкого уровня для формирования прерывания при снижении напряжения питания ниже установленной границы. В результате процессор успевает сохранить необходимые данные в энергонезависимой внешней памяти или выполнить другие необходимые инструкции для предотвращения неблагоприятных последствий, связанных с пропаданием питания. В нашей схеме данный сигнал подключен непосредственно к плюсовому выводу шины питания и не используется. Также не используется и выходной сигнал PWDACK, предназначенный для транзита сигнала, уведомляющего о снижении питания.

Наконец последний вывод процессора BMODE определяет интерфейс, через который будет производиться загрузка процессора. Если на этот вывод подан нулевой потенциал, загрузка процессора будет производиться через интерфейс BDMA, т.е. из байтовой памяти. В противном случае процедура загрузки будет производиться через интерфейс IDMA. В дальнейшем мы рассмотрим оба варианта загрузки. Для автоматизации процесса загрузки в схеме применен триггер, выполненный на элементах D4.1 и D4.2. В зависимости от источника сброса, триггер переключается в такое состояние, которое обеспечивает установку на выводе BMODE сигнала, необходимого для загрузки через соответствующий интерфейс.

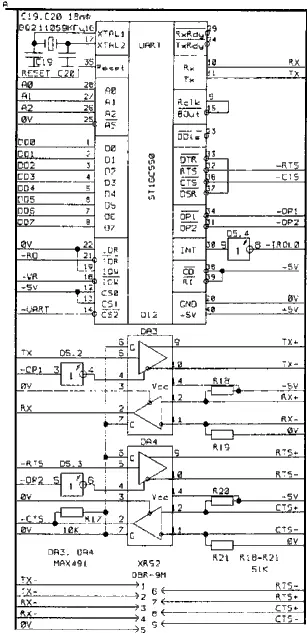

Еще одно внешнее устройство в качестве дополнения схемы приведено на рис. 3.5. Это дополнение схемы не является обязательным и может не распаиваться на основную плату. Но если появится необходимость оснащения рассмотренной выше схемы еще одним последовательным портом типа RS-422, это дополнение поможет в этом.

Рис. 3.5. Внешнее устройство в качестве дополнения схемы процессора

Как видно из рисунка, схема содержит интегрированную микросхему UART D12 с подключенными к ней резонатором BQ2 и вспомогательными конденсаторами C19, C20 для запуска внутреннего генератора. Программирование этой микросхемы производится через сигналы шины данных DD0–DD7. Выходные сигналы микросхемы UART подключены к приемопередатчикам — преобразователям уровней сигналов DA3 и DA4 для организации последовательного порта RS-422. Элементы D5.2 и D5.3 инвертируют выходные сигналы управления UART, обеспечивая отключение приемопередатчиков DA3 и DA4 в момент сброса самого UART или при включении.

Элемент D5.3 инвертирует выходной сигнал запроса прерывания от UART. Резисторы R17–R21 обеспечивают пассивное состояние сигналов при отключенной линии связи. Этот порт позволяет обмениваться информацией со 127 другими устройствами по аналогичному порту на расстоянии до 1200 метров. Все сигналы порта выведены на разъем XRS2.

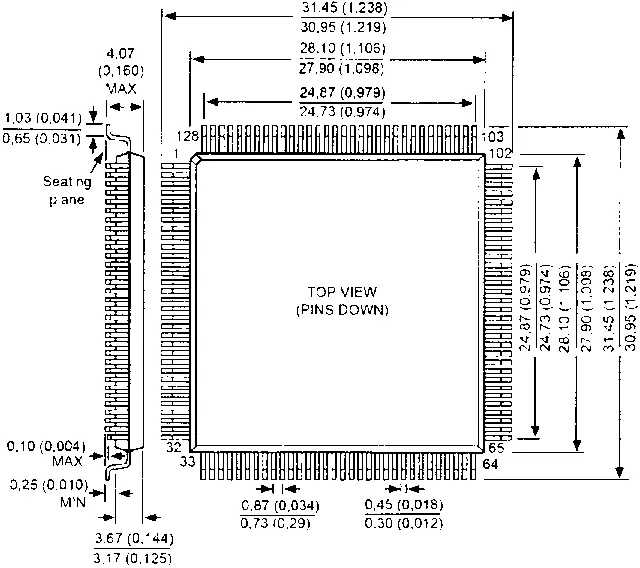

Вся схема может быть распаяна на небольшой макетной плате или на специально изготовленной плате с разработанной топологией электрических соединений. Для разработки топологии печатной платы необходимо создать файл посадочного места для компонента — процессора, который будет использоваться системой автоматического проектирования САПР. Чертеж корпуса процессора приведен на рис. 3.6.

Рис. 3.6. Корпус процессора

На нем даны все необходимые размеры в двух системах единиц измерения. В скобках приведены размеры в дюймах, а без скобок — в миллиметрах. Ввиду того, что процессор имеет большое количество выводов и мелкий шаг между ними, для изготовления электронных устройств с его применением может потребоваться разработка печатной платы. Однако некоторые умельцы используют другие хитрые приемы для установки таких компонентов на печатной плате. Одним из таких способов является наклейка фрагментов текстолита с контактными площадками по периметру установочного места компонента. После чего выводы компонента припаиваются к контактным площадкам этих фрагментов, и уже после этого тонкими проводниками осуществляется остальной монтаж всего устройства.

Читать дальшеИнтервал:

Закладка: