Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Выход ALU подключен к выходному регистру результата AR и через регистр обратной связи AF на вход ALU через мультиплексор. Регистр AF позволяет результату вычисления использоваться в качестве следующего операнда. Регистр AR имеет выход на шину DMD-BUS и R-BUS. В системе команд предусмотрена возможность чтения регистра AR посредством шины PMD-BUS аналогично двум предыдущим вариантам.

Любой из регистров ALU доступен для записи и чтения в течение цикла процессора (для чтения — в начале цикла, и для записи - в конце процессорного цикла). Таким образом, новое значение, записанное в конце одного цикла, может быть прочитано лишь в начале следующего. Это позволяет входным регистрам записать в ALU операнд в начале цикла и считать следующий операнд в конце того же цикла. Это также позволяет сохранить содержимое регистра результата в памяти и оперировать со следующим результатом в одном цикле.

Арифметико-логическое устройство имеет альтернативные (теневые) банки регистров AX, AY, AF и AR. На структурной схеме они изображены в виде теней. В конкретный момент времени доступен только один из типов банков. Дополнительный банк может быть использован для автоматического сохранения данных в регистрах ALU при быстром переключении на выполнение подпрограммы. В этом случае экономится время на сохранение текущих данных в памяти процессора.

Выбор главного или альтернативного банка регистров определяется битом 0 регистра режимов процессора MSTAT. Если этот разряд равен 0, то выбран главный банк, если он равен 1, то выбирается дополнительный банк.

Арифметико-логическое устройство выполняет набор стандартных арифметических и логических операций. Из арифметических операций АЛУ выполняет сложение, вычитание, отрицание, инкремент, декремент и вычисление модуля. Эти операции дополнены двумя примитивами деления, с помощью которых возможна реализация цикла многократного деления. Из логических операций АЛУ выполняет логическое сложение (OR), логическое умножение (AND), исключающее ИЛИ (XOR), и логическое отрицание (NOT). Стандартные операции ALU приведены в табл. 14.2.

Таблица 14.2 Стандартные операции ALU

| Операция | Назначение |

|---|---|

| R=X+Y | Сложение операндов X и Y |

| R=X+Y+CI | Сложение операндов X и Y с переносом |

| R=X-Y | Вычитание операнда Y из X |

| R=Y-X | Вычитание операнда X из Y |

| R=X-Y+CI-1 | Вычитание операнда Y из X с заемом |

| R=Y-X+CI-1 | Вычитание операнда X из Y с заемом |

| R= -X | Инверсия операнда X |

| R= -Y | Инверсия операнда Y |

| R=X+1 | Инкремент операнда X |

| R=Y+1 | Инкремент операнда Y |

| R=X-1 | Декремент операнда X |

| R=Y-1 | Декремент операнда Y |

| R=PASS X | Результат равен операнду X с установкой флагов регистра статуса ASTAT |

| R=PASS Y | Результат равен операнду Y с установкой флагов регистра статуса ASTAT |

| R=0 | Очистка результата |

| R=ABS X | Результат равен абсолютному значению операнда X (значение по модулю) |

| R=X AND Y | Логическое умножение операндов X и Y |

| R=X OR Y | Логическое сложение операндов X и Y |

| R=X XOR Y | Исключающее «ИЛИ» операндов X и Y |

| R=NOT X | Логическое отрицание X |

| R=NOT Y | Логическое отрицание Y |

В качестве условных записей операндов X, Y и R ALU, указанных в табл. 14.2, могут выступать следующие регистры:

- для X: AX0, АХ1, AR, MR0, MR1, MR2, SR0, SR1;

- для Y: AY0, AY1, AF;

- для R: AR и AF.

Регистры MR0, MR1, MR2 принадлежат умножителю MAC, а регистры SR0, SR1 устройству сдвига Shifter. Они доступны ALU по шине данных.

С целью обработки чисел с повышенной точностью, в ALU используются сигнал переноса CI (carry-in) и бит переноса AC (ALU carry). Операция сложения с переносом предназначена для сложения старших частей чисел, а операция вычитания с заемом — для их вычитания.

Регистр AR может работать в режиме насыщения. В этом режиме он принимает максимально возможное отрицательное или положительное значение, если операция заканчивается переполнением. Эта функция регистра AR становится возможной при установке в единицу разряда 3 регистра MSTAT. В табл. 14.3 показано содержимое регистра AR ALU в зависимости от флагов регистра состояния ASTAT при включенном, с помощью регистра MSTAT, режиме насыщения.

Таблица 14.3 Содержимое регистра AR ALU в зависимости от флагов регистра состояния

| AV (переполнение) | АС (перенос) | Содержимое AR |

|---|---|---|

| 0 | 0 | В соответствии с результатом ALU |

| 0 | 1 | В соответствии с результатом ALU |

| 1 | 0 | 0111111111111111 (максимальное положительное число) |

| 1 | 1 | 1000000000000000 (минимальное отрицательное число) |

Режим блокировки переполнения ALU разрешается при установке в единицу бита 2 регистра MSTAT. В этом режиме при переполнении ALU разряд AV устанавливается в единицу и при последующих операциях остается в этом состоянии. Таким образом, последующее переполнения уже не генерируются. Бит состояния AV можно очистить непосредственно с DMD шины путем записи в регистр состояния ASTAT нуля.

Арифметико-логическое устройство поддерживает операции деления. Деление осуществляется путем сложения и циклического сдвига чисел с помощью двух специальных примитивов деления DIVS и DIVQ. Команда DIVS вычисляет знаковый бит частного, а DIVQ вычисляет один бит частного. Данные команды применяются для деления знаковых или беззнаковых чисел. Алгоритм деления выполняет либо сложение, либо вычитание, основываясь на знаках делителя и частичного остатка. Остаток при этих операциях недоступен. При этом делитель и делимое должны быть одного типа. Обычная точность деления для 32-разрядного делимого, 16-разрядного делителя и 16-разрядного остатка реализуется за 16 циклов. Делитель может быть сохранен в регистре AX0, АХ1 или в любом регистре результатов R. Старший байт знакового делителя должен находиться либо в регистре AY1, либо в AF, а беззнакового делителя — в регистре AF. Младший байт делителя любого типа должен находиться в AY0. Остаток после деления будет записан в регистр AY0.

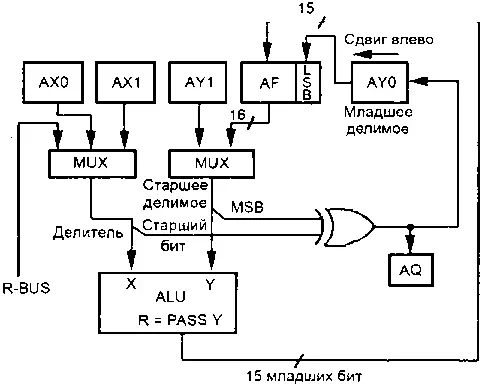

Первый из двух примитивов — это команда DIVS (деление-знак). Она предназначена для деления чисел со знаком. Структура операции DIVS показана на рис. 14.3.

Рис. 14.3. Структура операции DIVS

Данная операция вычисляет знаковый бит остатка, выполняя операцию «ИСКЛЮЧАЮЩЕЕ ИЛИ» для знаковых разрядов делителя и делимого.

Регистр AY0 сдвигается на одну позицию таким образом, чтобы знаковый разряд переместился в позицию LSB. Вычисленный знаковый разряд сохраняется в бит AQ регистра состояния. При делении чисел без знака операция DIVS не применяется. В этом случае бит AQ устанавливается в 0. Он показывает, что остаток должен быть положительным.

Читать дальшеИнтервал:

Закладка: