Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Когда процессор умножает два операнда в формате 1.15, в результате получается число в формате 2.30 (два знаковых и 30 дробных разрядов).

В дробном режиме MAC автоматически сдвигает результат на один бит влево перед пересылкой его в регистр результата MR. Этим сдвигом результат приводится к виду 1.31, который может быть округлен до формата 1.15.

В целочисленном режиме сдвига влево не происходит. Например, при умножении операндов в формате 16.0 результат представляется в виде 32.0.

Сдвиг влево в этом случае не нужен, т.к. он изменит числовое представление результата. В табл. 15.1 показаны форматы данных операндов и результата для вычислительных устройств процессора ADSP-2181.

Таблица 15.1 Форматы данных операндов и результата для вычислительных устройств процессора ADSP-2181

| Операции | Арифметические форматы | |

|---|---|---|

| Операнды | Результат | |

| Устройство ALU | ||

| Сложение | Знаковые числа или без знака | Установка флагов |

| Вычитание | Знаковые числа или без знака | Установка флагов |

| Логические операции | Двоичные строки | Тот же, что и операнды |

| Деление | Знаковые числа или без знака | Тот же, что и операнды |

| Переполнение ALU | Знаковые числа | Тот же, что и операнды |

| Бит коррекции ALU | 16-разрядные числа без знака | Тот же, что и операнды |

| Насыщение ALU | Знаковые числа | Тот же, что и операнды |

| Устройство MAC (дробные числа) | ||

| Умножение (P) | 1.15 знаковые числа /без знака | 32 разряда (2.30) |

| Умножение (MR) | 1.15 знаковые числа /без знака | 2.30, сдвинутый к 1.31 |

| Умножение с накоплением | 1.15 знаковые числа /без знака | 2.30, сдвинутый к 1.31 |

| Умножение с вычитанием | 1.15 знаковые числа /без знака | 2.30, сдвинутый к 1.31 |

| Насыщение MAC | Знаковые числа | Тот же, что и операнды |

| Устройство MAC (целые числа) | ||

| Умножение (P) | 1.15 знаковые числа /без знака | 32 разряда (32.0) |

| Умножение (MR) | 16.0 знаковые числа /без знака | 32.0 без сдвига |

| Умножение с накоплением | 16.0 знаковые числа /без знака | 32.0 без сдвига |

| Умножение с вычитанием | 16.0 знаковые числа /без знака | 32.0 без сдвига |

| Насыщение MAC | Знаковые числа | Тот же, что и операнды |

| Устройство сдвига Shifter | ||

| Логические сдвиги | Баз знака/двоичные строки | Тот же, что и операнды |

| Арифметические сдвиги | Знаковые числа | Тот же, что и операнды |

| Определение порядка | Знаковые числа | Тот же, что и операнды |

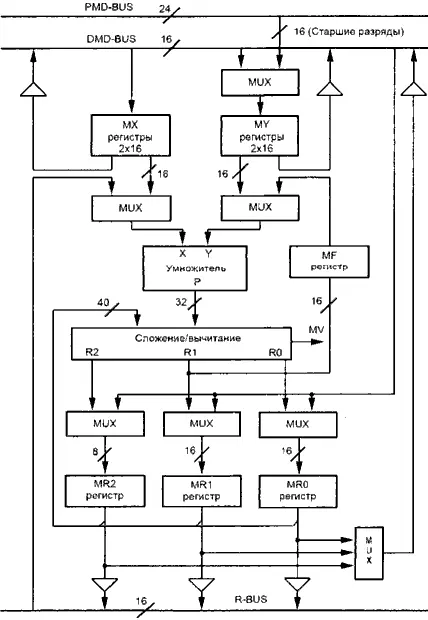

Рассмотрим подробнее содержимое устройства MAC. Его структурная схема приведена на рис. 15.1.

Рис. 15.1. Структурная схема MAC

MAC имеет два входных 16-разрядных порта X и Y и один 32-разрядный порт вывода результата P. 32-разрядный результат поступает в 40-разрядный блок сложения/вычитания, который либо прибавляет, либо вычитает текущий результат из регистра результата MR, либо передает текущий результат непосредственно в MR. Регистр MR имеет 40 разрядов. Фактически регистр MR состоит из трех регистров. Два из них, MR0 и MR1, являются 16-разрядными, а регистр MR2 8-разрядный. Мультиплексоры MUX позволяют коммутировать внутри устройства один из нескольких операндов.

Блок сложения/вычитания имеет более 32 разрядов для того, чтобы учесть промежуточные переполнения в ряде операций умножения с накоплением. Флаг MV (переполнение) устанавливается в единицу, если значение аккумулятора превышает 32 разряда.

Регистры ввода-вывода подобны регистрам ALU. Порт X может принимать данные из регистра MX или из любого другого регистра на R-шине результата. R-шина соединяет выходные регистры всех вычислительных модулей для непосредственного использования результатов вычислений в качестве входных операндов. Регистр MX состоит из двух регистров (MX0 и MX1).

Эти регистры читаются и записываются с DMD-шины. Организованы регистры MX0 и MX1 таким образом, что один из них поставляет множитель в блок умножения, а другой управляет DMD-шиной.

Порт Y принимает данные из регистра MY или регистра обратной связи MF. Регистр MY также разбит на два регистра (MY0 и MY1), доступ к которым осуществляется с DMD-шины и возможна запись с PMD-шины. Система команд предусматривает чтение этих регистров с помощью PMD-шины, но прямого доступа для этой операции нет, в этом случае используется устройство DMD-PMD обмена. Выводы регистра MY устроены аналогично MX.

Результат умножения поступает либо в блок сложения/вычитания, либо в регистры MY или MF. Регистр обратной связи MF позволяет результату вычисления в предыдущем цикле становиться операндом умножения на входе Y, в последующей операции. 40-разрядный регистр MR разделен на три регистра (MR0, MR1, MR2). Содержимое любого из них может быть выведено на DMD-шину или R-шину и записано с DMD-шины.

Любой из регистров MAC может быть прочитан и записан в одном цикле. Чтение данных происходит в начале цикла, а запись - в конце цикла. Прочитанное содержимое регистра в начале одного цикла записывается в конце предыдущего, следовательно, новое значение регистра может быть прочитано только в течение следующего цикла. Такой механизм позволяет входному порту предоставлять операнд для MAC в начале цикла и оперировать со следующим значением из памяти в конце того же цикла. Это относится и к выходному регистру.

Регистры MR, MF, MX, MY продублированы в теневых банках. Одновременно процессору может быть доступен лишь один из банков. Теневой банк регистров может быть активизирован для чрезвычайно быстрого контекстного переключения. Таким образом, новая задача, типа подпрограммы обработки прерывания, может выполняться без сохранения текущих данных в памяти, благодаря использованию теневых банков. Выбор первичного или теневого банка регистров определяется установкой нулевого разряда в регистре MSTAT состояний процессора. Если этот разряд установлен в 0, то выбран первичный банк.

Теперь рассмотрим операции вычислительного устройства MAC, входные форматы данных, обработку переполнения и насыщения.

Набор стандартных операций MAC приведен в табл. 15.2.

Таблица 15.2 Набор стандартных операций MAC

| Операция | Назначение |

|---|---|

| X*Y | Умножение X на Y |

| MR+X*Y | Умножение X на Y и сложение с MR |

| MR-X*Y | Умножение X на Y и вычитание из MR |

| 0 | Очистка MR |

Как было сказано выше, сигнальный процессор ADSP-2181 обеспечивает два режима работы операций умножения с накоплением. Первый из них — режим работы с дробными числами в формате 1.15. Второй — режим работы с целыми числами в формате 16.0.

Читать дальшеИнтервал:

Закладка: