Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]

- Название:Искусство схемотехники. Том 3 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002954-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредотачивается на тонких аспектах проектирования и применения электронных схем.

На русском языке издается в трех томах. Том 3 содержит сведения о микропроцессорах, радиотехнических схемах, методах измерения и обработки сигналов, принципах конструирования аппаратуры и проектирования маломощных устройств, а также обширные приложения.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 3 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

УСАПП не имеет никакого представления о биполярных уровнях интерфейса RS-232, поэтому на всех упомянутых линиях следует использовать драйверы и приемники уровней RS-232. В течение десятилетий в качестве интерфейсных микросхем для уровней RS-232 использовались классические модели биполярных счетверенных драйвера 1488 и приемника 1489; однако для нашего прибора мы выбрали КМОП-микросхему МАХ233 (сдвоенный драйвер/приемник), большим достоинством которой является наличие встроенных удвоителей напряжения и инверторов, что позволяет ограничиться единственным источником питания +5 В. Заметьте, что мы не связывались с линиями управления модемом (RTS, CTS, DSR, DTR); вообще их, как правило, игнорируют, используя вместо аппаратного программное квитирование (Ctrl-S, Ctrl-Q), включаемое в поток данных.

Программное обеспечение. Как уже отмечалось, режимы работы УСАПП устанавливаются командами программы. Байт, посылаемый в УСАПП в командном режиме (сигнал D/C ' имеет низкий уровень), интерпретируется УСАПП, как команда управления и устанавливает рабочий режим. Таким образом можно определить вид передачи (синхронная или асинхронная), число стоп-бит, контроль четности или нечетности и т. д. Простые УСАПП вчерашнего дня имели всего один управляющий регистр и программировались легко; хитроумные микросхемы вроде 8530 содержат буквально десятки регистров и для программирования требуют квалификации доктора философии. К сожалению, такова цена, которую вы платите за исключительную гибкость мощных БИС аппаратной поддержки микропроцессора.

Для иллюстрации сказанного рассмотрим последовательность команд инициализации микросхемы 8530 для работы в следующем режиме: асинхронная последовательная передача по каналу А, скорость 1200 бод, 8 бит, без контроля четности, 1 стоп-бит; кроме того, мы запретим прерывания. Полная процедура инициализации длинна и утомительна; мы приведем программу целиком, однако во всей красе рассмотрим лишь один-два важнейших командных байта. В табл. 11.6 перечислены регистры записи и чтения микросхемы 8530, доступ к которым, как мы уже объясняли, осуществляется в два этапа: сначала передается номер регистра в качестве команды (D/C ' в низком состоянии), а затем происходит запись в регистр (или чтение из него).

Таблица 11.6. Регистры микросхем Zilog 8530

Регистр · Функция

_____________________

Регистры чтения

RR0· Состояние буферов приема-передачи и внешнее состояние

RR1· Состояние условия специального приема

RR2· Немодифицированный вектор прерывания (канал А); модифицированный вектор (канал В)

RR3· Биты незавершенных прерываний

RR8· Буфер приема

RR10· Общее состояние

RR12· Счетчик скорости пересылки (младший байт)

RR13· Счетчик скорости пересылки (старший байт)

RR15· Информация о прерывании, внешнее/состояние

Регистры записи

WR0· Инициализация, указатели

WR1· Прерывания и пересылка, определение режима

WR2· Вектор прерывания

WR3· Прием, параметры и управление

WR4· Общие параметры и режимы

WR5· Передача, параметры и управление

WR6· Символы синхронизации или адресное поле SDLC

WR7· Символ синхронизации или флаг SDLC

WR8· Буфер передачи

WR9· Управление и сброс прерывания ведущего

WR10· Биты общего управления передачи/приема

WR11· Управление режимом генератора

WR12· Счетчик скорости пересылки (младший байт)

WR13· Счетчик скорости пересылки (старший байт)

WR14· Биты общего управления

WR15· Управление прерыванием, внешнее/состояние

Для буферов передачи и приема (WR8 и RR8) двухэтапная процедура не приемлема, так как эти регистры используются при пересылке каждого байта; для них достаточно простых операций чтения или записи при D/C ' в высоком состоянии. Точно так же, байт состояния буфера требует непосредственного доступа, поскольку чтение его флага обычно осуществляется при каждой пересылке байта данных; в микросхеме 8530 предусмотрено чтение RR0 с помощью простой операции чтения команды/состояния (D/C ' в низком состоянии). Ниже мы рассмотрим все это подробнее на основе простых программ на языке ассемблера.

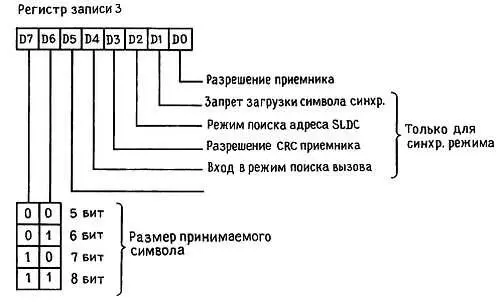

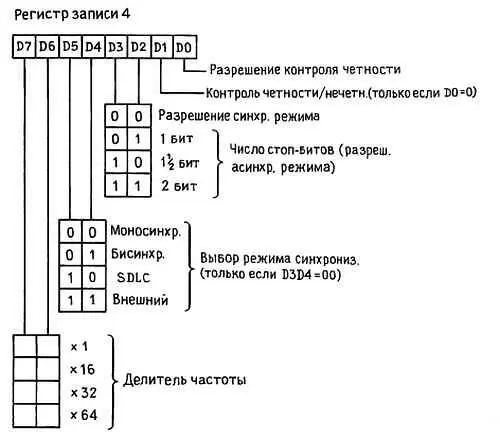

Каждый бит каждого регистра что-то означает. Например, на рис. 11.26 можно найти регистры WR3 и WR4, с помощью которых устанавливаются различные коммуникационные характеристики.

Рис. 11.26. Два регистра, используемые для инициализации микросхемы Zilog 8530.

В регистре WR3 к асинхронным операциям относятся только биты D0 разрешения приемника, D5 разрешения аппаратного квитирования (см. след. раздел) с помощью сигналов управления модемом CTS и DCD, а также два старших бита, определяющие число бит на символ. Остальные биты связаны с синхронными режимами, которые мы собираемся выключить соответствующим выбором D2-D3 в WR4. Таким образом, мы устанавливаем (D7, D6) = (1,1), D5 = 0 и D0 = 1, т. е. в WD3 мы посылаем шестнадцатеричный байт С1. С помощью WR4 мы задаем режим генератора x16 (минимальный делитель для асинхронных операций — УСАПП должен выполнять опрос сигнала каждого бита в его середине, поэтому частота входного генератора делается кратной частоте передачи), 1 стоп-бит на символ (используется всегда, за исключением устаревшего стандарта на телетайпную передачу со скоростью 110 бод), отсутствие контроля четности; получается шестнадцатеричный байт 44. Заметьте, что состояние битов D5-D4 не имеет значения, так как они управляют синхронной передачей; произвольно также состояние D1 (контроль четности или нечетности), если D0 (включение контроля) равен 0. Заметьте также, что установка 1 стоп-бита на символ (что имеет смысл только для асинхронного режима) автоматически выключает синхронный режим, а вместе с ним и все биты регистра управления, определяющие синхронные операции (например, D4-D1 в регистре WR3). Таким же образом можно управиться и с остальными управляющими регистрами. Это довольно скучная работа, в процессе которой легко допустить ошибки.

В табл. 11.7 приведены правильные, как мы надеемся, значения байтов (мы их тщательно проверили!).

Таблица 11.7. Инициализация последовательного порта 8530 1)

Регистр · Байт 2)· Результат

________________________________

WR0· (Указатель регистра) · Используется для доступа к WR1-WR15

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]](/books/607005/paul-horovits-iskusstvo-shemotehniki-tom-3-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)