Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]

- Название:Искусство схемотехники. Том 3 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002954-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредотачивается на тонких аспектах проектирования и применения электронных схем.

На русском языке издается в трех томах. Том 3 содержит сведения о микропроцессорах, радиотехнических схемах, методах измерения и обработки сигналов, принципах конструирования аппаратуры и проектирования маломощных устройств, а также обширные приложения.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 3 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

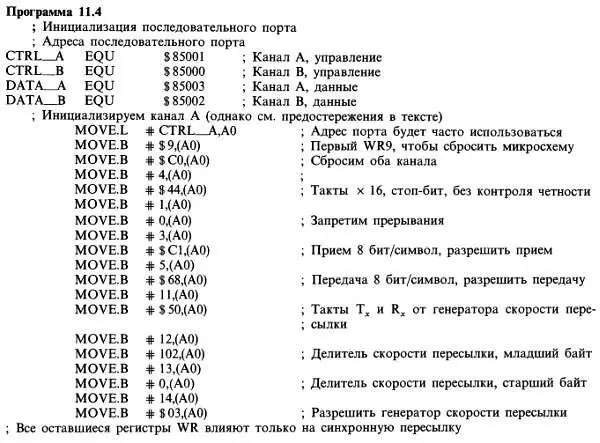

WR1· 00 · Запрет прерываний

WR2· XX · Вектор прерываний (если разрешены)

WR3· С1 · 8 бит, разрешение приема

WR4· 44 · х15, 1 стоп-байт без контроля

WR5· 68 · 8 бит, разрешение передачи

WR6· XX · Символ синхронизации (только синхронный режим)

WR7· XX · Символ синхронизации (только синхронный режим)

WR8· (Буфер передачи) · Передаваемые данные (прямой доступ с D/C ' = 1)

WR9· СО · Сброс

WR10· XX · Режимы синхронных операций

WR11· 50 · Такты приема/передачи от генератора скорости пересылки

WR12· 102 10· Делитель скорости пересылки - старший байт

WR13· 00 · Делитель скорости пересылки - младший байт

WR14· 03 · Разрешение генератора скорости пересылки

WR15 · XX · Режимы прерываний (если разрешены)

_____

1) Асинхронный режим, 1200 бод, 8 бит, без контроля четности.

2) XX-произвольное состояние; все числа шестнадцатеричные, кроме WR12.

Обратите внимание на состояние XX (произвольное) для регистров, игнорируемых нами, в силу того, что мы не используем ни прерываний, ни синхронного режима. Регистр WR9 выполняет полный сброс микросхемы, который должен предшествовать любым другим командам. С помощью регистров WR12 и WR13 устанавливается 16-разрядное значение делителя частоты передачи, которое для микросхемы 8530 дается выражением частота передачи = f такт /[2 (режим генератора) x (делитель + 2)]. Таким образом, при частоте генератора 4 МГц и режиме генератор x16 для скорости передачи 1200 бод получаем делитель 102 10(фактически скорость передачи составит 1201,92 бод, что весьма близко к заданному значению). При выбранной нами частоте генератора возможны все стандартные скорости передачи вплоть до 9600 бод (для этой скорости делитель должен быть равен 13).

Заметьте, что в вашем распоряжении все многочисленные режимы работы УСАПП, устанавливаемые соответствующими последовательностями инициализирующих управляющих байт. Микросхема 8530, как и все УСАПП, обеспечивает также синхронную коммуникацию в различных режимах со скоростями до 1 Мбит/с; это особенно полезно для пересылки данных между двумя процессорами. Для нашего прибора такой способ пересылки не имеет смысла в силу ограниченного объема оперативной памяти, однако он может оказаться полезным при подключении жесткого диска.

Обратите внимание на необходимость пересылки из ЦП в УСАПП правильной последовательности инициализирующих байт до того, как начнут передаваться какие-либо последовательные данные, как это было и в случае параллельного порта 8536; в нашем примере последовательный порт не использовался, так что мы опустили его инициализацию. Программа 11.4 дает понятие о процедуре инициализации. Сложность программы (включая декодирование таблиц с данными с целью определения управляющих байтов) — это цена, которую вы платите за исключительную гибкость БИС поддержки микропроцессора.

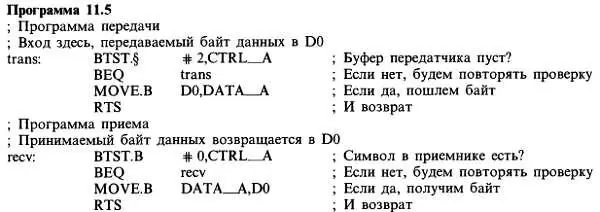

После того как с помощью управляющих регистров установлен режим работы УСАПП, можно передавать и принимать байты данных с помощью циклов ЦП записи и чтения при высоком уровне сигнала D/C ' . С целью определения наличия нового, ожидающего приема в ЦП байта данных или возможности пересылки в УСАПП нового байта для его дальнейшей передачи следует опрашивать регистр состояния (при низком уровне D/C ' ), конкретно D0 в регистре RR0 в первом случае, и D2 в том же регистре во втором.

В дополнение к этому по другим битам регистра состояния можно судить о фиксации ошибки четности, потере принимаемых данных и т. д. Часто эти страшные удары судьбы можно игнорировать и смело идти вперед. В программе 11.5 приведены фрагменты пересылки данных при том же, что и раньше, отображении регистров на адресное пространство.

Учтите, что эти примеры, в которых используется программный ввод-вывод с проверкой состояния (см. разд. 10.06–10.08 ), иллюстрируют работу простейших программных драйверов. В них работа ЦП останавливается на время циклического опроса флага состояния. Использование механизма прерываний позволяет повысить эффективность работы ЦП; это особенно справедливо для операций ввода. Микросхема 8530 может возбуждать прерывания по любому указанному условию; от нее даже можно получить в качестве подтверждения выбранный вами 8-битовый вектор, если использовать линии подтверждения прерывания (IEI, IEO, INTACK). Все эти возможности реализуются с помощью управляющих байтов инициализации.

Микросхемы параллельного ввода-вывода (PIO).В состав нашего микропроцессорного прибора была включена многофункциональная микросхема параллельного порта (такого рода схемы часто объединяются с одним или несколькими таймерами). Использованная нами микросхема 8536 принадлежит тому же семейству, что и микросхема последовательного порта 8530 и использует схожие интерфейс с процессором и протокол настройки. Хорошие микросхемы параллельных портов позволяют программировать для каждого бита в отдельности направление передачи и режим (с фиксацией, с открытым стоком, с инверсией). Протокол передачи данных также можно запрограммировать; например, в микросхеме 8536 можно разрешить векторизуемые прерывания по любому сочетанию входных бит. Можно также выбрать один из четырех режимов квитирования (см. ниже).

Микросхемы РIO, как и все периферийные БИС, разрабатываются на базе n МОП- и КМОП-технологий, причем в новых разработках используется в основном последняя. С выходов таких схем можно снять, как правило, несколько мА, однако n МОП-схемы, в отличие от КМОП, обеспечивают лишь доли мА. Поэтому они обычно используются совместно с микросхемами мощных драйверов, позволяющих подключать к ним нагрузку, требующую значительных токов. Не пытайтесь подключать реле непосредственно к выходу микросхемы РIO (см. наши замечания относительно микросхем среднего уровня интеграции в разделе «Фиксаторы и D-регистры»).

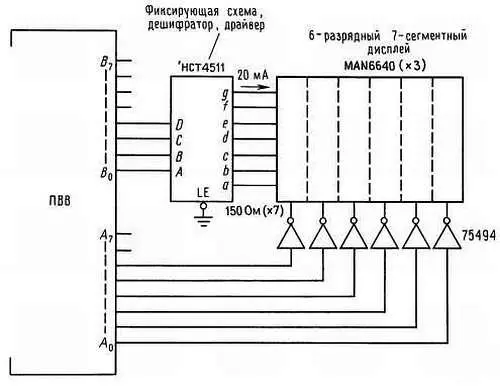

На рис. 11.27 показан пример реальной схемы, конкретно для управления 6-разрядным дисплеем.

Рис. 11.27. Управление мультиплексированным дисплеем от РIO.

Конечно, вам придется написать программу для периодического вывода последовательных десятичных чисел, а также и «шагающего бита» через порт А, не забыв запретить прерывания на время вывода, чтобы предотвратить мерцание. Другой, более простой способ управления многоразрядным ЭЛД-дисплеем в микропроцессорной системе заключается в использовании чего-то вроде семейства «интеллектуальных дисплеев» фирмы Siemens-дисплейных секций, отображаемых на память, и выглядящих с точки зрения ЦП просто как участки памяти (см. рис. 9.24); поскольку такие дисплеи запоминают выводимые числа, запись в них требуется выполнять только при смене отображаемого числа.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 3 [Изд.4-е]](/books/607005/paul-horovits-iskusstvo-shemotehniki-tom-3-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)