Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]

- Название:Искусство схемотехники. Том 2 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002338-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредоточивается на тонких аспектах проектирования и применения электронных схем. На русском языке издается в трех томах.

Том 2 содержит сведения о прецизионных схемах и малошумящей аппаратуре, о цифровых схемах, о преобразователях информации, мини- и микроЭВМ и микропроцессорах.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 2 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Несколько версий. С помощью ПЛИС можно спроектировать одну единственную схему и затем изготавливать несколько различных версий устройства, выпуская платы с различно запрограммированными ПЛИС. Например, вы могли бы иметь компьютер, который содержит кристаллы памяти либо на 256К, либо на 1М, причем изменения касались бы только ПЛИС.

Скорость и комплектация. При использовании ПЛИС проектирование схемы в общем случае можно выполнить гораздо быстрее (если вы, разумеется, хорошо ориентируетесь в этой области). Более того, вам потребуется всего несколько типов ПЛИС, а не несколько дюжин типов стандартных схем средней интеграции. Действительно, всего две новых ПЛИС GAL (базовая матричная логика) благодаря программируемости своей внутренней архитектуры (и связей) заменят целый набор ПМЛ. В частности, 20-выводная GAL16V8 и 24-выводная GAL20V8 каждая может имитировать по 21 стандартных ПМЛ. Более того, их можно запрограммировать как «помесь» ПМЛ (например, нечетное число регистров).

Расширение функций ПМЛ. Входы/выходы. Выводы выходов с 3 состояниями, подключенные внутри кристалла к входам матрицы И, можно использовать в качестве входов. Например, ПМЛ 16L8, показанная на рис. 8.45, имеет 16 входов (прямых и инверсных) на матрицу И; 10 из них обозначены как входные выводы, а 6 являются цепями обратной связи с выходов с 3 состояниями. Эти 6 выводов можно превратить в «перманентные» входы путем блокировки соответствующего выхода (подключить пару прямой/инверсный к управлению И); с другой стороны, эти входы могут работать в двух направлениях за счет блокировки формирователей с 3 состояниями, соответствующими некоторой логической переменной.

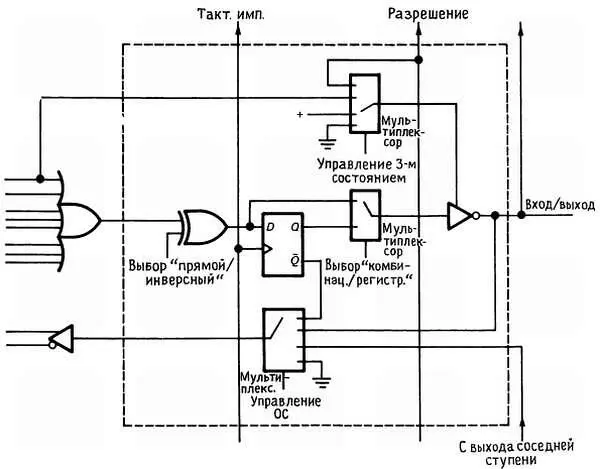

«Супер-ПМЛ». Ранее мы уже отмечали, что наиболее гибкая программируемая логика соответствует оригинальным ПМЛ, среди которых самыми известными являются стираемые КМОП-варианты фирм Lattice, VTI, Altera и др. ПМЛ GAL фирмы Lattice, например, использует программируемую логику с электрическим стиранием, так что вы можете перепрограммировать кристалл. Более того, выходные структуры («макроячейки») сами программируемы, — каждый выход может быть как регистром, так и комбинационной схемой с прямым и инверсным выходом. Похожей программируемостью обладают линия активации 3-го состояния и линия включения обратной связи (последняя может подключаться до и после буфера с 3 состояниями или к соседнему выходу); см. рис. 8.84. В результате, вы можете имитировать любую обычную 20-выводную ПМЛ, используя только один корпус GAL16V8 (и любую обычную 24-выводную ПМЛ, используя GAL20V8). Это позволяет сохранять перечень комплектующих изделий в управляемых границах. Фирма Altera имеет линию программируемой КМОП-логики, которая допускает ультрафиолетовое стирание по типу ЭППЗУ (в корпусе ИС над кристаллом имеется окно из кварцевого стекла). Такие устройства называют СПЛИС — стираемая программируемая логическая интегральная схема.

Рис. 8.84. Программируемая макроячейка базовой матричной логики.

Самая маленькая ИС из этой серии (ЕР320) имеет выходные макроячейки и имитирует все 20-выводные ПМЛ, точно также, как GAL16V8. Более того, она маломощна в отличие от «прожорливых» оригинальных ПМЛ (см. ниже). Наконец, фирма Altera выпускает несколько более крупных СПЛИС, а также программируемые микросеквенсеры и т. п. Фирмы Cypress и VTI также выпускают стираемую программируемую КМОП-логику с макроячейками. Другим подходом к созданию программируемой логики является ОЗУ-подобная вентильная матрица фирмы Xilinx. Впечатляющие кристаллы этой матрицы содержат огромные блоки конфигурируемой логики, причем конфигурация связей хранится во внутреннем ОЗУ кристалла (энергозависимая память). Эта память загружается от внешней памяти после включения питания либо от микропроцессора; кроме того, она может самозагружаться с использованием памяти типа энергонезависимого ПЗУ.

Скорость и мощность. Оригинальная ПМЛ на биполярных транзисторах, разработанная на фирме Monolithic Memories (и быстро скопированная National и AMD) потребляла значительный ток — около 200 мА для 16L8/16R8, и имела задержку распространения 40 нс. Последующие биполярные ПМЛ «половинной мощности» были вполне приемлемы — 90 мА и 35 нc. Однако самые быстрые ПМЛ потребуют все еще уйму мощности; например, время распространения ПМЛ 16R8D и 16Р8-7 фирмы AMD составляет соответственно 10 и 7,5 нс, но потребляют они 180 мА. (макс). КМОП-приборы существенно лучше: GAL (GAL20V8-15Q) «1/4 мощности» фирмы Lattice потребляют 45 мА при задержке 15 нс, ЕР320-1 фирмы Altera обладают задержкой 25 нс при токе 5 мА. Но что более важно для маломощных устройств, так это то, что кристаллы фирмы Altera (а также ПМЛ серии Ζ фирмы AMD) могут работать в резервном режиме с «нулевой мощностью». Конструкторы будущих структур программируемой логики, наверняка, сохранят эту здоровую тенденцию к повышению скорости и снижению мощности; современная программируемая логика, этот «пожиратель ватт», начинает уходить в прошлое!

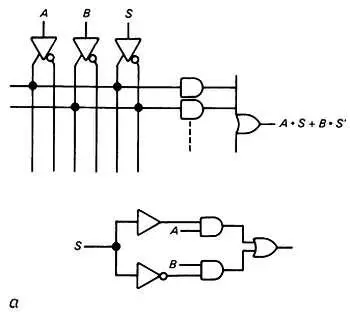

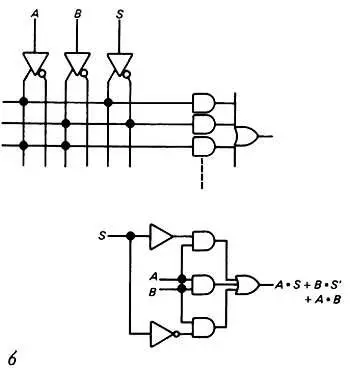

Выбросы. ПЛИС, конечно, удивительная вещь, но вы можете, ненароком, оказаться в затруднительном положении, если не будете помнить о возможности логических состязаний. На рис. 8.85 показан 2-входовый мультиплексор, выполненный самым обычным способом; показаны ПМЛ — реализация и эквивалентная схема.

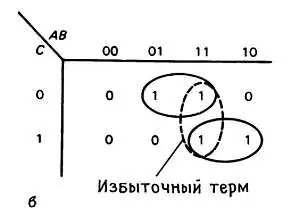

Рис. 8.85. Исключение глитча в ПМЛ; а— 2-входовый мультиплексор; б— для исключения глитча добавляется избыточный терм произведения; в— карта Карно с избыточным термом.

Здесь все выглядит как-будто прекрасно, но схема имеет один изъян: когда оба входа ( А и В ) находятся в состоянии высокого уровня, а линия ВЫБОР меняет состояние, на выходе, как показано, возможен выброс. Это объясняется тем, что внутренние задержки по цепям S и S' могут быть не равны, что приведет к появлению переходного состояния, в котором на одном из входов вентилей И будет низкий уровень. Избавиться от этого можно, использовав избыточный терм А*В, который будет гарантировать отсутствие выбросов, в чем вы можете легко убедиться.

Упражнение 8.33.Покажите, что дополнительный терм устраняет все возможности для появления выбросов.

Упражнение 8.34.Какие логические термы следует добавить к 4-входовому мультиплексору (рис. 8.75) для устранения выбросов.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]](/books/607006/paul-horovits-iskusstvo-shemotehniki-tom-2-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)