Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]

- Название:Искусство схемотехники. Том 2 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002338-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредоточивается на тонких аспектах проектирования и применения электронных схем. На русском языке издается в трех томах.

Том 2 содержит сведения о прецизионных схемах и малошумящей аппаратуре, о цифровых схемах, о преобразователях информации, мини- и микроЭВМ и микропроцессорах.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 2 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

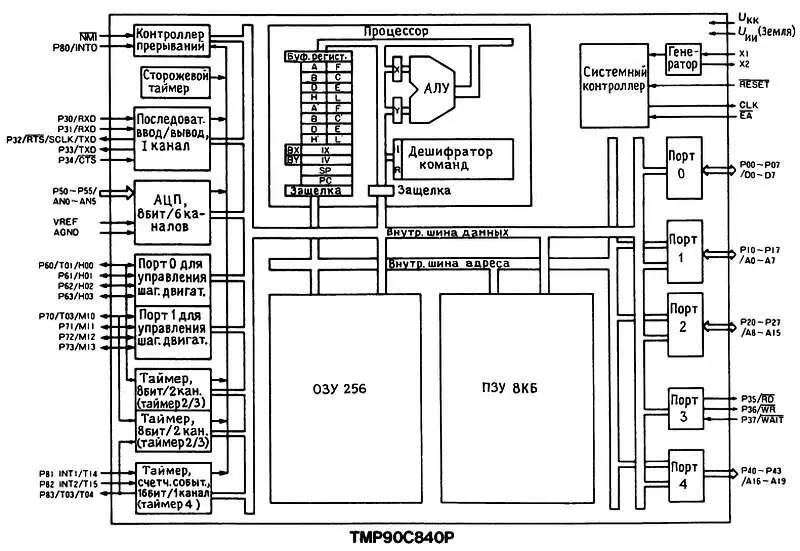

Микропроцессоры.Самым выдающимся примером «чуда» БИС является микропроцессор (компьютер на кристалле). На одной вершине находятся мощные цифровые приборы, подобные 68020/30 и 80386/486 (32-разрядные быстрые процессоры с предвыборной команд, виртуальной памятью, мощнейшие арифметические сопроцессоры) и кристаллы, подобные MicroVAX, которые эмулируют существующие большие компьютеры. На другой вершине — однокристальные процессоры с различными функциями ввода, вывода и памяти, работающие самостоятельно. Например, один из последних образцов, это TLCS-90 фирмы Toshiba (рис. 8.86), представляющий маломощный КМОП микроконтроллер с 6-канальным 8-разрядным АЦП, встроенными таймерами, ОЗУ и ПЗУ, 20-двунаправленными цифровыми линиями ввода/вывода, последовательным портом и двумя портами для управления шаговыми двигателями. Этот прибор больше предназначен для задач управления, чем для проведения вычислений.

Рис. 8.86. Однокристальный микропроцессор со схемами ввода/вывода.

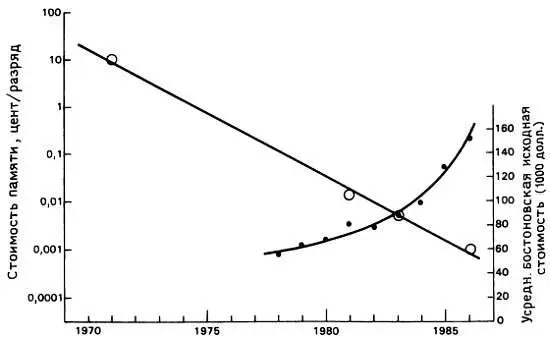

Революция в микропроцессорах не проходила в одиночестве, и мы видим удвоение компьютерной мощности и размера памяти (в настоящее время 1 Мбит, сравните с 16 Кбит на кристалле на время написания первого издания этой книги) каждый год, в то же время цены развиваются драматически (рис. 8.87). Наряду с укрупнением и улучшением процессоров и памяти, последние работы сверхскоростных приборов и больших параллельных архитектур обещают более волнующие события в последующие годы.

Рис. 8.87. Закон Кремниевой Долины: кривая обучения.

Некторые типовые цифровые схемы

Благодаря усилиям полупроводниковой промышленности цифровые схемы удивительно легки и приятны. Почти нет случаев, когда приходится класть цифровую схему на «хлебную доску», как это часто происходит с линейными схемами. Вообще говоря, единственными серьезными проблемами являются синхронизация и шумы.

Мы в последующем расскажем об этом. Здесь уместно проиллюстрировать синхронизацию на нескольких примерах последовательностных схем. Некоторые из этих функций могут быть выполнены с помощью БИС, однако рассматриваемые реализации сделаны на хорошем уровне и позволяют проиллюстрировать, какого типа схемы можно строить с помощью имеющихся средств.

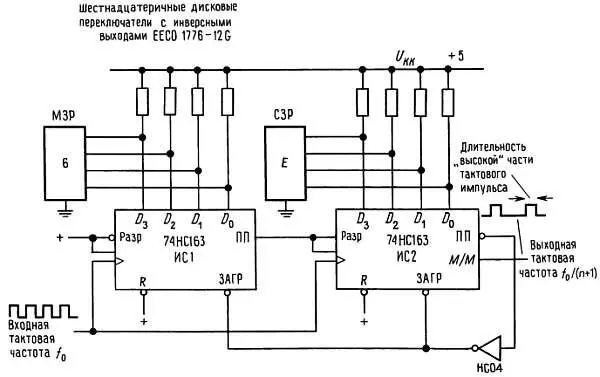

Изображенная на рис. 8.88 схема на каждые n входных тактовых импульсов вырабатывает один выходной импульс. Значение n есть 8-разрядное число, которое вы задаете с помощью двух барабанных шестнадцатеричных переключателей. Схемы `163 являются 4-разрядными синхронными суммирующими счетчиками с синхронной загрузкой (когда вход LD' - низкий) через D-входы. Идея состоит в загрузке дополнительного кода, счете вверх до FF n и перезагрузке по следующему тактовому импульсу. Поскольку мы сформировали значение перезагрузки с помощью источника +5 (с общим заземленным выводом переключателя), то эти уровни являются отрицательно-истинными для отображения набора переключателей, это означает, что загружаемые значения интерпретируются как истинные положительные, равные дополнительному до 1 значению, установленному на переключателях.

Рис. 8.88. Счетчик по модулю n.

Упражнение 8.35.Путем вычисления истинного положительного значения, которое будет установлено на переключателях рис. 8.88, докажите истинность последнего утверждения.

Работа схемы совершенно очевидна. Для каскадирования синхронных счетчиков вы соединяете все тактовые входы вместе, затем соединяете выход «максимальный счет» каждого счетчика с разрешением следующего счетчика. Для схемы `163 выход RCO ( ripple-clock output — выход переполнения ПП) выставляет ВЫСОКИЙ уровень при максимальном счете, разрешая второму счетчику посредством установления разрешения (ВЫСОКОГО уровня) на входах ENT и ENP (Разр). Таким образом, ИС1 повышает свое значение на каждый тактовый импульс, а ИС2 повышает свой счет на каждый тактовый импульс после того, как ИС1 насчитает значение F n . Таким образом, два счетчика считают пока не достигнут состояния FF n , в этой точке входы загрузки LD' устанавливаются в истинное значение. Это приводит к синхронной предзагрузке на следующем такте. Здесь мы выбрали счетчики с синхронной загрузкой для того, чтобы избежать логических состязаний (и короткого импульса RCO), которые могут возникнуть в счетчике с асинхронной загрузкой. К сожалению, счетчик при этом делит на n + 1, а не на n .

Упражнение 8.36. Объясните, что произойдет, если счетчик с асинхронной загрузкой (например, `191) заменить на счетчик с синхронной загрузкой `163. Покажите, в частности, как могут образовываться короткие импульсы. Покажите также, что предыдущая схема делит на n + 1, в то время как при асинхронной загрузке будет осуществляться деление на n (если схема вообще будет работать).

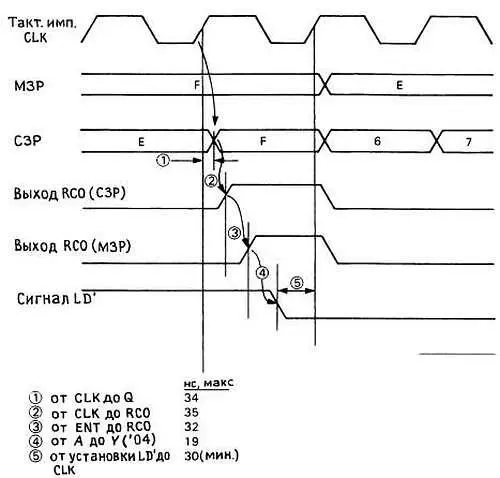

Временная диаграмма.До какой максимальной частоты может считать наш счетчик? Схема 74НС163 имеет гарантированную максимальную частоту счета f макс 27 МГц. Однако в нашей схеме существуют дополнительные временные задержки, связанные с каскадным соединением (ИС2 должна «узнавать», что ИС1 уже достигла максимального счета за время до следующего тактового импульса), и с соединением «загрузка при переполнении». Для изображения максимальной частоты, при которой гарантируется работа схемы, мы должны добавить задержку для наихудшего случая и быть уверенным, что остается достаточно времени да переустановку. Посмотрите на рис. 8.89, где мы изобразили временную диаграмму, показывающую последовательность загрузки, которая выполняется при максимальном счете.

Рис. 8.89. Временная диаграмма счетчика по модулю nи расчет максимальной скорости работы.

Изменение сигнала с НИЗКОГО на ВЫСОКИЙ уровень на каком-либо выходе Q следует за положительным фронтом тактового сигнала максимум через 34 нc. Это интересно (но не относится к делу), что загружаемая последовательность использует выход RCO (переноса); сигнал RCO следует за положительным фронтом тактового импульса, что при максимальной частоте счета составляет максимум 35 нc. Сигнал переноса RCO ИС2 появляется после наличия входного разрешения (при условии, конечно, что это происходит при максимальном счете) максимум через 32 нc. Схема 74НС04 добавляет задержку максимум в 19 нc для генерации сигнала ЗАГРУЗКА' (LD'), которая должна предшествовать сигналу такта ( i setup ) как минимум на 30 нc. Что приводит нас к следующему тактовому импульсу; таким образом 1/ f макс = (35 + 32 + 19 + 30) нc, или f макс = 8,6 МГц. Что значительно меньше, чем максимально гарантируемая частота счета одного 74НС163.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]](/books/607006/paul-horovits-iskusstvo-shemotehniki-tom-2-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)