Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]

- Название:Искусство схемотехники. Том 2 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002338-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредоточивается на тонких аспектах проектирования и применения электронных схем. На русском языке издается в трех томах.

Том 2 содержит сведения о прецизионных схемах и малошумящей аппаратуре, о цифровых схемах, о преобразователях информации, мини- и микроЭВМ и микропроцессорах.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 2 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

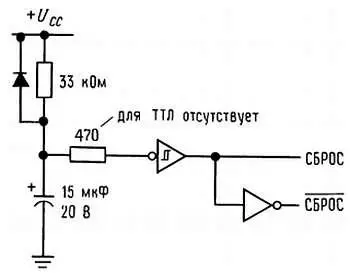

Рис. 8.93. Схема для формирования сигнала сброса при включении питания.

Логические гонки.Здесь скрываются многие коварные ловушки. Классический случай логических гонок был описан в разд. 8.19 на примере синхронизатора импульсов. В любом случае, когда вентили управляются сигналами от триггеров, необходимо убедиться в том, что в схеме не может возникнуть ситуация, в которой к моменту тактирования триггера вентиль открывается, а по истечении задержки на триггере закрывается. Сигналы, возникающие на входах триггеров, не должны быть задержанными по отношению к тактовым импульсам (еще одно преимущество синхронной системы!). В общем случае задерживайте такты, но не информацию. Необычно легко проглядеть возможность возникновения логических гонок.

Метастабильные состояния.Как уже отмечалось, триггер и любое тактируемое устройство могут сбиться, если изменение сигналов на информационных входах произойдет менее чем за время t уст до возникновения тактового импульса. В худшем случае выход триггера будет буквально совершать колебания в окрестности логического порога в течение нескольких микросекунд (для сравнения: нормальная величина задержки распространения элементов ТТЛ составляет 20 нc). Разработчики логических схем это обычно не принимают во внимание, но подобная проблема может возникнуть в быстродействующих системах, когда потребуется синхронизовать асинхронные сигналы. Такую ситуацию считают виновной во многих таинственных сбоях ЭВМ, но мы смотрим на это предположение скептически. В этом случае требуется лишь установить цепочку синхронизаторов или «детектор метастабильных состояний», который будет сбрасывать триггер.

Скос фронтов тактовых импульсов.Скос фронтов тактовых импульсов оказывает большее влияние на схемы КМОП, чем на ТТЛ. Такая проблема возникает в том случае, когда для тактирования нескольких соединенных между собой устройств используется сигнал с большим временем нарастания (рис. 8.94).

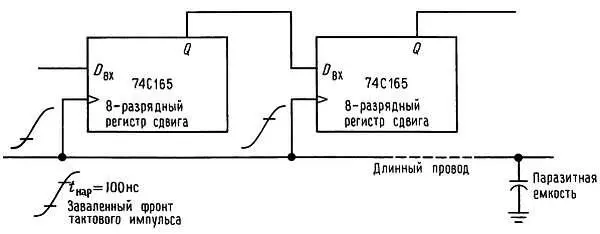

Рис. 8.94. Временной сдвиг из-за завала тактовых импульсов.

В рассматриваемом примере два регистра сдвига тактируются фронтом с большим временем нарастания. Это время обусловлено емкостной нагрузкой выхода КМОП, который имеет относительно высокий импеданс (порядка 500 Ом при работе от источника +5 В). Проблема возникает из-за того, что порог срабатывания у первого регистра может оказаться ниже, чем у второго, в результате чего его сдвиг произойдет раньше и последний бит первого регистра будет потерян. Дело еще осложняется тем, что значения пороговых напряжений для устройств на КМОП колеблются в очень широком диапазоне (фактически они могут принимать любое значение в пределах от 1/3 до 2/3 U cc и они принимают!). В подобной ситуации самое лучшее — это располагать корпуса микросхем рядом, тем самым избегать большой емкостной нагрузки по тактовым входам.

Говоря в общем, тактовые входы каких-либо цифровых микросхем должны всегда тщательно обрабатываться. Например, тактовые линии с шумом или «звоном» должны всегда очищаться с помощью вентиля (возможно, с входным гистерезисом) до подачи на синхронизируемый кристалл. У вас, вероятно, возникали проблемы с линиями синхронизации, которые поступали с другой платы или с другого логического семейства. Например, медленная логика 4000 В или 74С, питающая быстрые семейства НС или АС, наверняка вызовет проблемы перекоса импульсов или кратных переходов.

Укороченные импульсы.В разд. 8.29 при рассмотрении счетчиков по модулю n мы отмечали, что в том случае, когда счетчики должны сбрасываться собственным входным сигналом, необходимо ввести задержку для того, чтобы предотвратить появление укороченного импульса. То же самое относится и к импульсам записи в счетчики или регистры сдвига. Укороченные импульсы часто доставляют неприятности, приводят схему к работе на границе устойчивости и вызывают периодические сбои. При разработке схемы следует исходить из наихудшего значения для задержки.

Неопределенные правила.Когда полупроводниковая промышленность нащупывала свой путь, начиная с простейших схем резисторно-транзисторной логики 1960 г., затем ТТЛ- и ТТЛШ-семейства, до высокопроизводительных современных КМОП-семейств, было недопонято значение стандартизации выводов, спецификаций и функциональности. Как пример, схема 7400 (И-НЕ) имела свои выводы вентилей, а схема 7401 (ИЛИ-НЕ с открытым коллектором) имела отличные от нее расположения выводов вентилей. Это создавало такую путаницу, что побудило выпустить «мутант»-схему 7403, которая представляет собой схему 7401, но с разводкой вентилей, как у 7400. Подобное недоразумение случилось со схемой 7490 (двоично-десятичный счетчик) с расположением контактов питания по середине корпуса, а не в углах. (Как ни смешно, но контакты питания, расположенные посредине корпуса, «возвратились» в быстродействующих схемах КМОП, для уменьшения индуктивности и улучшения изоляции.)

Важным наследством этой ранней анархии является «всякая всячина» неопределенных правил, которых мы придерживаемся. Например, популярный `74D-триггер существует в каждом логическом семействе; подача одновременно сигналов установки и сброса приводит к высокому уровню на обоих выходах в каждом семействе, кроме 74С, где это приводит к низкому уровню на выходах! Это не совсем неопределенное правило, поскольку если вы внимательно посмотрите в хорошую документацию, то найдете непоследовательность. На техническом жаргоне это называют «Попался!» ( gotcha ). Другим любимым нашим примером этого «попался!» является схема `96: 5-разрядный сдвиговый регистр с хитрыми входами загрузки; они могут устанавливаться, но не сбрасываться. Подлинным неопределенным правилом, а фактически очень важным является «время перемены». Это такое количество времени, которое вы должны ожидать после снятия асинхронного входного сигнала для полной гарантии синхронизации тактируемого элемента.

Проектировщиков кристаллов не беспокоило это обстоятельство (хотя проектировщики схем всегда хотели это знать), пока логические семейства, выпускавшиеся ранее 1980 г., не были обойдены улучшенными ТТЛШ и быстрыми КМОП-семействами. Если вы проектируете с применением более ранней логики (например, 74С), наш совет — быть консервативным, например, предполагайте, что время перемены такое же, как время установки данных хотя обычно оно меньше. Так например, у D-триггера 74НС74 минимальное время распространения определяется в 5 не, в то время как минимальное время установки данных составляет 20 нc.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]](/books/607006/paul-horovits-iskusstvo-shemotehniki-tom-2-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)