Лекции по схемотехнике

- Название:Лекции по схемотехнике

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:нет данных

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Лекции по схемотехнике краткое содержание

Лекции по схемотехнике - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

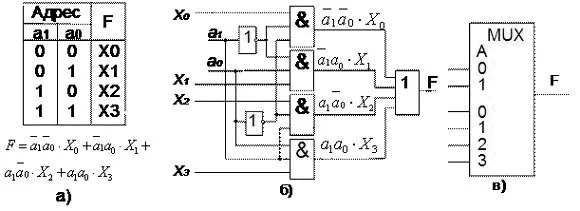

В простейшем случае при двухразрядном адресном коде (n=2) максимальное число входных адресных линий равно N=2 n=4. Таблица истинности такого мультиплексора приведена на рисунке 33,а.

Рисунок 33 Мультиплексор 4:1 а) — Таблица истинности;

б) — Функциональная схема; в) — Условное графическое обозначение.

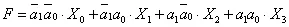

Характеристическое уравнение такого мультиплексора, записанное в соответствии с таблицей истинности, имеет вид:

Из полученного уравнения следует, что в состав функциональной схемы мультиплексора входят два инвертора, четыре схемы «И» и одна схема «ИЛИ» (Рисунок 33,б). Здесь адресными (управляющими) входами являются а 1, а 0, а информационными — Х0, Х1, Х2, Х3 .

Условное графическое обозначение мультиплексора, в соответствии с ГОСТ 2.743-91, приведено на рисунке 33,в.

В настоящее время промышленность выпускает МС, в серии которых входят мультиплексоры с n=2, 3 и 4 адресными входами. При n=2 выпускаются сдвоенные четырёхканальные (2 n=4) мультиплексоры, число входных информационных сигналов которых равно 2 n+2 n=8.

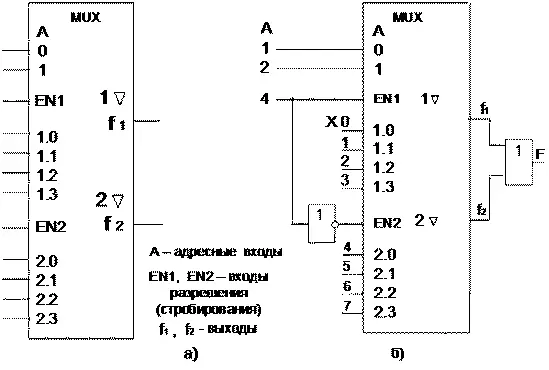

УГО сдвоенного 4-канального мультиплексора со стробированием К555КП12 приведено на рисунке 34,а.

Рисунок 34 Сдвоенный 4-канальный мультиплексор К555КП12 а) и 8-канальный мультиплексор на его основе б).

Входы стробирования используются для построения мультиплексоров (коммутаторов) с k2 n-информационными входами, k=2, 3, 4…

Схема мультиплексора 8:1 на основе сдвоенного 4-канального мультиплексора со стробированием приведена на рисунке 34,б.

Если подавать на информационные входы X iпостоянные уровни, соответствующие лог. «0» или лог. «1», то на выходе мультиплексора можно получить любую желаемую функцию переменных управляющего кода. При этом число переменных в реализуемой выходной функции будет равно разрядности управляющего кода.

В общем случае на информационные входы можно подавать не постоянные логические уровни, тогда на выходе мультиплексора реализуется логическая функция с большим числом переменных.

4.3.2 Дешифраторы-демультиплексоры

Демультиплексор — это функциональный узел, осуществляющий управляемую коммутацию информацию, поступающую по одному входу, на N выходов. Таким образом, демультиплексор реализует операцию, противоположную той, которую выполняет мультиплексор.

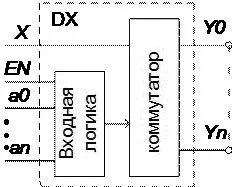

Обобщённая схема демультиплексора приведена на рисунке 35. В общем случае число выходных линий N определяется количеством адресных входов n и равно N=2 n.

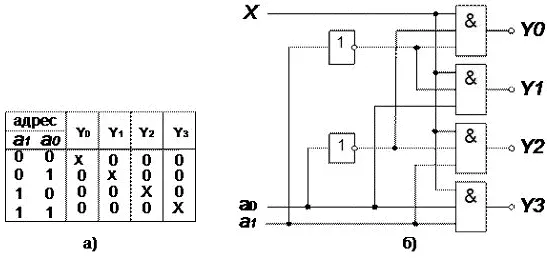

Для случая n=2 функционирование демультиплексора осуществляется в соответствии с таблицей истинности, приведённой на рисунке 36,а.

Рисунок 35 Обобщённая схема демультиплексора

Рисунок 36 Таблица истинности — а) и функциональная схема 4-канального демультиплексора — б)

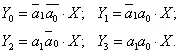

Из таблицы истинности записываем характеристические уравнения демультиплексора:

Соответствующая этим уравнениям функциональная схема демультиплексора приведена на рисунке 36,б. Она имеет в своём составе два инвертора и четыре элемента «И».

Сравнивая таблицы истинности и функциональные схемы демультиплексора и дешифратора, легко увидеть схожесть их функций. Если функция X=1 постоянно, то демультиплексор выполняет функции дешифратора. Учитывая схожесть выполняемых функций, микросхемы дешифраторов и демультиплексоров имеют одинаковое условное обозначение — ИЕ, называются «Дешифратор-демультиплексор» и могут выполнять функции и дешифратора и демультиплексора.

В качестве примера рассмотрим микросхему К155ИД4, УГО которой приведено на рисунке 37,а. Это сдвоенный 4-канальный дешифратор-демультиплексор. Каждая секция имеет один информационный вход (D и Ē), один вход разрешения  , четыре выхода

, четыре выхода  и два общих адресных входа (a 1, a 0). Возможные способы включения и режимы работы показаны на рисунке 36,б.

и два общих адресных входа (a 1, a 0). Возможные способы включения и режимы работы показаны на рисунке 36,б.

Рисунок 37 Микросхема К155ИД4 а) и возможные режимы её работы б).

Наличие у МС прямого и инверсного информационных входов позволяет простым их объединением получить третий адресный разряд а 2, а двух инверсных входов разрешения — общий вход разрешения дешифратора 3:8 или информационный вход демультиплексора 1:8.

Рассмотренную выше микросхему дешифратора К155ИД3 можно использовать в качестве демультиплексора с форматом 1:16. При этом входы разрешения дешифрации используются в качестве основного информационного входа X, а адресные входы и выходы используются по прямому назначению.

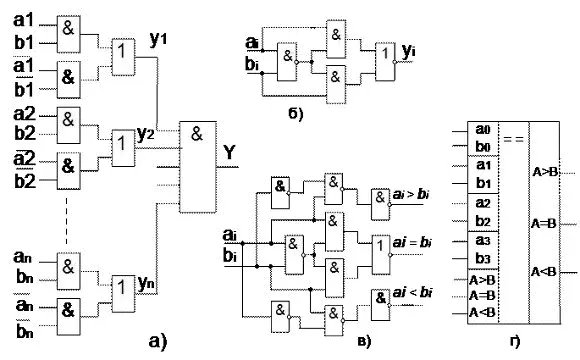

4.4 Устройства сравнения кодов. Цифровые компараторы

Устройства сравнения кодов предназначены для выработки выходного сигнала в случае, когда поступающие на их входы коды двух чисел оказываются одинаковыми.

Числа A и B считаются равными, если разрядные коэффициенты чисел A и B оказываются одинаковыми, то есть, если a i=b i =1 или a i=b i =0. Эти равенства можно привести к одному:  . Поскольку это равенство выполняется для каждого разряда, то выходной сигнал Y можно представить в виде логической функции:

. Поскольку это равенство выполняется для каждого разряда, то выходной сигнал Y можно представить в виде логической функции:

где n — число разрядов.

Рисунок 38 Устройства сравнения кодов: а) — структурная схема; б) — минимизированный вариант схемы сравнения в одном разряде; в) — одноразрядный компаратор; г) — УГО 4-разрядного компаратора.

Структурная схема устройства сравнения кодов, составленная на основании приведённого выше уравнения приведена на рисунке 38,а. Выходной сигнал Y=1 будет иметь место только при условии, если будут единичными результаты сравнения во всех разрядах сравниваемых чисел.

Читать дальшеИнтервал:

Закладка: