Лекции по схемотехнике

- Название:Лекции по схемотехнике

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:нет данных

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Лекции по схемотехнике краткое содержание

Лекции по схемотехнике - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

В структуре типа 3D выборка элемента памяти из массива производится по двум координатам. Код адреса разрядностью n делится на две половины и используются два дешифратора: по строкам и по столбцам. При этом число выходов двух дешифраторов равно 2 n/2+2 n/2=2 n/2+1. Если n=8, то число выходов дешифраторов равно 2 4+2 4=32, а количество элементов памяти равно 2 n/2·2 n/2=2 n=256. В структуре 2D-типа, как уже было отмечено выше, потребовался бы более сложный дешифратор на 256 выходов.

Таким образом, с помощью двух дешифраторов, имеющих небольшое число выходов, осуществляется доступ ко всем элементам памяти микросхемы.

Структура 3D может применяться и в ЗУ с многоразрядной организацией, принимая при этом «трёхмерный» характер. В этом случае несколько матриц управляются от двух дешифраторов, относительно которых матрицы включены параллельно.

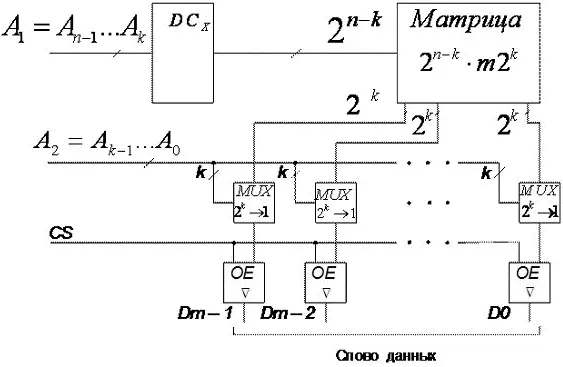

состоит из дешифратора, который выбирает целую строку. Однако, в отличие от структуры 2D , длина строки многократно превышает разрядность хранимых слов. При этом число строк уменьшается и, следовательно, уменьшается число выводов дешифратора.

Выбор строк матрицы памяти производится с помощью старших разрядов адреса A n -1… A k . Остальные k разрядов используются для выбора необходимого m-разрядного слова из множества слов, содержащихся в строке.

Рисунок 66 Структура ЗУ типа 2DM для ROM

Это выполняется с помощью мультиплексоров, на адресные входы которых подаются коды A k -1… A 0. Длина строки равна m ·2 k , где m — разрядность слов.

Из каждого отрезка строки, длиной 2 k , мультиплексор выбирает один бит. На выходах m мультиплексоров формируется выходное m -разрядное слово. По разрешению сигнала CS, поступающего на входы OE управляемых буферов с тремя выходными состояниями, выходное слово передаётся на внешнюю шину.

6.3 Оперативные запоминающие устройства

6.3.1 Типы оперативных запоминающих устройств

В зависимости от способа хранения информации оперативные запоминающие устройства (ОЗУ) подразделяются на статические и динамические. В статических ОЗУ (Static RAM — SRAM) запоминающими элементами являются триггеры, сохраняющие своё состояние, пока схема находится под питанием и нет новой записи данных.

В динамических ОЗУ (Dynamic RAM — DRAM) данные хранятся в виде зарядов конденсаторов, образуемых элементами МОП-структур. Саморазряд конденсаторов ведёт к разрушению данных, поэтому они должны периодически (каждые несколько миллисекунд) регенерироваться. В то же время плотность упаковки динамических элементов памяти в несколько раз превышает плотность упаковки достижимую в статических RAM.

Регенерация данных в статических ЗУ осуществляется с помощью специальных контроллеров. Разработаны также ЗУ с динамическими запоминающими элементами, имеющие внутреннюю встроенную систему регенерации, у которых внешнее поведение относительно управляющих сигналов становится аналогичным поведению статических ЗУ. Такие ЗУ называются квазистатическими.

В целом динамические ЗУ характеризуются наибольшей информационной ёмкостью и невысокой стоимостью, поэтому именно они используются как основная память ЭВМ.

Статические ОЗУ делятся на асинхронные и тактируемые.

В асинхронных ЗУ сигналы управления могут задаваться как импульсами, так и уровнями. Например, сигнал разрешения работы  может оставаться неизменным и разрешающим на протяжении многих циклов обращения к памяти.

может оставаться неизменным и разрешающим на протяжении многих циклов обращения к памяти.

В тактируемых ЗУ некоторые сигналы обязательно должны быть импульсными. Например, сигнал разрешения работы  в каждом цикле обращения должен переходить из пассивного состояния в активное, то есть должен формироваться фронт этого сигнала в каждом цикле. Асинхронные ЗУ могут использоваться в качестве тактируемых.

в каждом цикле обращения должен переходить из пассивного состояния в активное, то есть должен формироваться фронт этого сигнала в каждом цикле. Асинхронные ЗУ могут использоваться в качестве тактируемых.

Статические ЗУ в 4…5 раз дороже динамических и приблизительно во столько же раз меньше по информационной ёмкости. Их достоинством является высокое быстродействие. Область применения относительно дорогостоящих статических ОЗУ в системах обработки информации определяется именно их высоким быстродействием. Типичной областью применения статических ОЗУ в ЭВМ являются схемы КЭШ-памяти.

Запоминающими элементами статических ОЗУ служат триггеры с цепями установки и сброса. Триггеры можно реализовать по любой схемотехнологии (ТТЛШ, И²Л, n-МОП, КМОП и др.), в соответствии с которой разработаны разнообразные схемы ЗУ с различными параметрами.

6.3.2 Основные параметры ЗУ

Важнейшими параметрами ЗУ являются информационная ёмкость и быстродействие.

Информационная ёмкость — максимально возможный объём хранимой информации. Выражается в битах или словах (в частности, в байтах). Бит хранится запоминающим элементом (ЗЭ), а слово — запоминающей ячейкой (ЗЯ), т.е. группой ЗЭ, к которой возможно лишь одновременное обращение.

Быстродействие (производительность) ЗУ оценивают временами записи, считывания и длительностями циклов записи/чтения.

Время записи — интервал после появления сигнала записи и установлением ЗЯ в состояние, задаваемое входным словом.

Время считывания — интервал между моментами появления сигнала чтения и слова на выходе ЗУ. Циклы записи и чтения — это время между двумя последовательностями записи или чтения. Длительности циклов могут превышать времена записи и чтения, так как после этих операций может потребоваться время для восстановления начального состояния ЗУ.

Кроме основных (эксплуатационных или измеряемых) параметров, ЗУ характеризуются рядом режимных параметров, обеспечение которых необходимо для нормального функционирования ЗУ. Поскольку ЗУ имеют несколько управляющих сигналов, то для них задаются не только длительности, но и взаимное положение во времени.

6.3.3 Внешняя организация и временные диаграммы статических ОЗУ

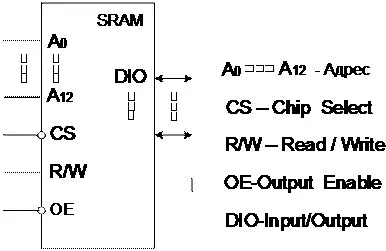

В номенклатуре статических ЗУ представлены микросхемы с одноразрядной и словарной организацией. Внешняя организация статического ЗУ ёмкостью 64 Кбита (8К×8) показана на рисунке 68.

Один из возможных наборов сигналов ЗУ.

Рисунок 68 Пример внешней организации статического ЗУ

A — адрес. Разрядность n определяется числом ячеек ЗУ, т.е. максимально возможным числом хранимых в ЗУ слов N=2 n , а n =log 2 N . Например, ЗУ с ёмкостью 8К слов имеет 13-разрядные адреса, выражаемые словами A=a 12 a 11 a 10… a 0, а с ёмкостью 64К слов — 16-разрядные адреса: A=a 15 a 14 a 13… a 0.

Читать дальшеИнтервал:

Закладка: