Лекции по схемотехнике

- Название:Лекции по схемотехнике

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:нет данных

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Лекции по схемотехнике краткое содержание

Лекции по схемотехнике - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Входные токи элемента, а следовательно, и токи нагрузки ЭСЛ малы: I 0 ВХ ≈0, ток I 1 ВХ равен базовому току транзистора, работающего на границе области насыщения, а не в области насыщения. Поэтому нагрузочная способность элемента велика и коэффициент разветвления достигает 20 и более.

Поскольку логический перепад невелик, то нестабильность напряжения источника питания существенно влияет на помехоустойчивость ЭСЛ. Для повышения помехоустойчивости в схемах ЭСЛ заземляют не отрицательный полюс источника питания, а положительный. Это делается для того, чтобы большая доля напряжения помехи падала на большом сопротивлении R эи только малая её доля попадала на входы схемы.

При совместном использовании ЛЭ ЭСЛ и ТТЛ между ними приходится включать специальные микросхемы, которые согласуют уровни логических сигналов. Их называют преобразователями уровней (ПУ).

Высокое быстродействие ЭСЛ обусловлено следующими основными факторами:

1 Открытые транзисторы не находятся в насыщении, поэтому исключается этап рассасывания неосновных носителей в базах.

2 Управление входными транзисторами осуществляется от эмиттерных повторителей предшествующих элементов, которые, имея малое выходное сопротивление, обеспечивают большой базовый ток и, следовательно, малое время открывания и закрывания входных и опорного транзисторов.

3 Малый логический перепад сокращает до минимума время перезарядки паразитных емкостей элемента.

Все эти факторы в комплексе обеспечивают малое время фронта и среза выходного напряжения элементов ЭСЛ.

Для ЭСЛ характерны следующие средние параметры: U пит =–5В; U 1=–(0,7–0,9)В; U 0=–(1,5–2)В; tЗ Д.ср =3–7 нс; P пот =10–20 мВт.

Перспективными считаются серии К500 и К1500, причём серия К1500 относится к числу субнаносекундных и имеет время задержки распространения менее 1 нс. (Таблица 8).

Таблица 8 Параметры основных серий ЛЭ ЭСЛ

| Параметры | Серии | |

|---|---|---|

| К500 | К1500 | |

| Входной ток I 0 ВХ ,мА | 0,265 | 0,35 |

| Входной ток I 1 ВХ , мА | 0,0005 | 0,0005 |

| Выходное напряжение U 0 ВЫХ , В | -1,85…-1,65 | -1,81…-1,62 |

| Выходное напряжение U 1 ВЫХ , В | -0,96…-0,81 | -1,025…-0,88 |

| Выходное пороговое напряжение, В: | ||

| U 0 ВЫХ.пор | -1,63 | -1,61 |

| U 1 ВЫХ.пор | -0,98 | -1,035 |

| Время задержки распространения, нс | 2,9 | 1,5 |

| Допустимое напряжение помехи, В | 0,125 | 0,125 |

| Коэффициент разветвления K РАЗ | 15 | — |

| Напряжение питания, В | -5,2; -2,0 | -4,5; -2,0 |

| Потребляемая мощность на элемент, мВт | 8…25 | 40 |

3.4 Транзисторная логика с непосредственными связями (ТЛНС)

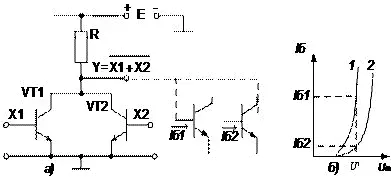

В схеме элемента ТЛНС сопротивление нагрузки включено в цепь соединенных коллекторов двух транзисторов (Рисунок 15,а). Входные сигналы X1 и X2 подаются на базы этих транзисторов. Если X1 и X2 одновременно равны «лог 0», то оба транзистора закрыты и на выходе схемы будет высокий потенциал Y=1. Если хотя бы на один, или на оба входа, подать высокий потенциал «лог 1», то один или оба транзистора открыты и на выходе схемы будет низкий потенциал Y=0. Таким образом, схема выполняет операцию ИЛИ-НЕ.

Рисунок 15 ЛЭ НСТЛ а) и входные характеристики транзисторов нагрузки б).

Как видно, схема элемента НСТЛ предельно проста, однако у неё есть существенный недостаток. Когда на выходе элемента установлен потенциал лог. «1», на базы транзисторов нагрузок, как показано на рисунке 15,а пунктиром, подаётся постоянный потенциал U ¹. Из-за разброса параметров транзисторов (см. рисунок 15,б), токи баз транзисторов могут существенно различаться. В результате один из транзисторов может войти в глубокое насыщение, а другой — находиться в линейном режиме. При этом уровни «лог.1» будут существенно различаться, что неизменно приведёт к сбоям в работе устройства в целом. Поэтому схема ЛЭ НСТЛ применяется только на транзисторах, управляемых напряжением.

3.5 Интегральная инжекционная логика

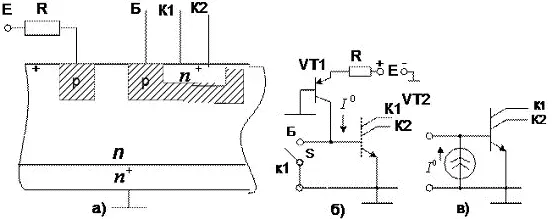

Элементы интегральной инжекционной логики (И²Л) не имеют аналогов в дискретной схемотехнике и могут быть реализованы только в интегральном исполнении (рисунок 16,а). Элемент И²Л состоит из двух транзисторов: горизонтальный p-n-p-транзистор выполняет роль инжектора, а вертикальный многоколлекторный n-p-n-транзистор работает в режиме инвертора. Общая область n-типа служит базой p-n-p-транзистора, а также эмиттером n-p-n-транзистора и подключается к «заземлённой» точке. Коллектор p-n-p-транзистора и база n-p-n-транзистора также являются общей областью. Эквивалентная схема приведена на рисунке 16,б.

Рисунок 16 Транзистор с инжекционным питанием: а — структурная схема, б — эквивалентная схема, в — эквивалентная схема с генератором тока.

В цепь эмиттер-база инжектора подаётся напряжение питания U ПИТ . Минимальное напряжение источника определяется падением напряжения на эмиттерном переходе: U КЭ.нас =0,7 В. Но для стабилизации тока эмиттера I 0последовательно с источником включается резистор R и берут напряжение источника питания U ПИТ =1…1,2 В. При этом p-n-переход эмиттер-база VT1 открыт и имеет место диффузия дырок к коллекторному переходу. По мере движения к коллектору часть дырок рекомбинируют с электронами, но их значительная часть достигает коллекторного перехода и, пройдя через него, попадают в p-базу инвертора (транзистора VT2). Этот процесс диффузии, т.е. инжекции дырок в базу идёт постоянно, независимо от входного воздействия.

Если напряжение на базе VT2 U вх = U 0, что соответствует замкнутому состоянию ключа S, дырки, попадающие в p-базу инвертора, беспрепятственно стекают к отрицательному полюсу источника питания. В цепи коллектора транзистора VT2 ток не протекает и это эквивалентно разомкнутому состоянию коллекторной цепи VT2. Такое состояние выходной цепи соответствует напряжению лог. «1».

При U вх = U 1(ключ S разомкнут) дырки в p-базе инвертора накапливаются. Потенциал базы начинает повышаться и соответственно понижаются напряжения на переходах VT2 до тех пор, пока эти переходы не откроются. Тогда в коллекторной цепи транзистора VT2 будет протекать ток и разность потенциалов между эмиттером и коллектором инвертора (транзистора VT2) будет близка к нулю, т.е. этот транзистор представляет собой короткозамкнутый участок цепи, и это состояние будет соответствовать уровню лог. «0». Таким образом, рассмотренный элемент выполняет роль ключа.

Читать дальшеИнтервал:

Закладка: