Лекции по схемотехнике

- Название:Лекции по схемотехнике

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:нет данных

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Лекции по схемотехнике краткое содержание

Лекции по схемотехнике - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

При практическом применении ЛЭ ТТЛ неиспользованные входы можно оставлять свободными. Однако при этом снижается помехоустойчивость из-за воздействия наводок на свободные выводы. Поэтому их обычно или объединяют между собой, если это не ведёт к превышению для предшествующего ЛЭ, или подключают к источнику питания +5 В через резистор R=1 кОм, ограничивающий входной ток. К каждому резистору можно подключать до 20 входов.

3.2.3 Элементы ТТЛШ

С целью увеличения быстродействия элементов ТТЛ, в элементах ТТЛШ используются транзисторы Шотки, представляющие собой сочетание обычного транзистора и диода Шотки, включённого между базой и коллектором транзистора. Поскольку падение напряжения на диоде Шотки в открытом состоянии меньше, чем на обычном p-n-переходе, то большая часть входного тока протекает через диод и только его малая доля втекает в базу. Поэтому транзистор не входит в режим глубокого насыщения.

Следовательно, накопление носителей в базе из-за их инжекции через коллекторный переход практически не происходит. В связи с этим имеет место увеличение быстродействия транзисторного ключа с барьером Шотки в результате уменьшения времени нарастания тока коллектора при включении и времени рассасывания при выключении.

Среднее время задержки распространения сигнала элементов ТТЛ с диодами Шотки (ТТЛШ) примерно в два раза меньше по сравнению с аналогичными элементами ТТЛ. Недостатком ТТЛШ является меньшая по сравнению с аналогичными элементами ТТЛ помехоустойчивость U + пом из-за большего значения U 0и меньшего U пор .

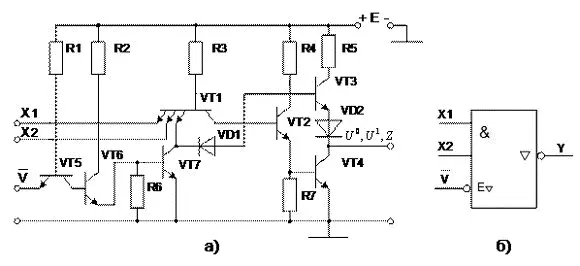

3.2.4 Элементы ТТЛ с тремя выходными состояниями —

имеют дополнительный вход V — вход разрешения (рисунок 13,а). При подаче на этот вход напряжения U 0транзистор VT5 открыт и насыщен, а транзисторы VT6 и VT7 закрыты и поэтому не влияют на работу логического элемента. В зависимости от комбинации сигналов на информационных входах на выходе ЛЭ может быть сигнал с уровнем «лог. 0» или «лог. 1». При подаче на вход V напряжения с уровнем «лог. 1» транзистор VT5 закрывается, а транзисторы VT6 и VT7 открываются, напряжение на базе транзистора VT3 уменьшается до уровня U БЭ.нас + U д, транзисторы VT2, VT3, VT4 закрываются и ЛЭ переходит в высокоимпедансное (третье) состояние, то есть отключается от нагрузки.

На рисунке 13,б показано УГО этого элемента. Значок ∇ указывает на то, что выход имеет три состояния. Значок E ∇«Разрешение третьего состояния» указывает, что сигналом  =0 ЛЭ переводится в третье (высокоомное) состояние.

=0 ЛЭ переводится в третье (высокоомное) состояние.

Для уменьшения помех по цепи питания в точках подключения к шинам групп ЛЭ устанавливают развязывающие керамические конденсаторы ёмкостью порядка 0,1 мкФ на один корпус. На каждой плате между цепью питания и общей шиной 1–2 электролитических конденсатора ёмкостью 4,7–10 мкФ.

Рисунок 13 Логический элемент ТТЛ И-НЕ с тремя выходными состояниями а) и его УГО б).

В таблице 7 приведены параметры некоторых серий ЛЭ ТТЛ.

Таблица 7 Параметры некоторых серий логических элементов ТТЛ

| ПАРАМЕТРЫ | СЕРИИ | ||||

|---|---|---|---|---|---|

| Универсальные | Высокого быстродействия | Микромощные | |||

| 133, 155 | К531 | КР1531 | К555 | Кр1533 | |

| Входной ток I 0 ВХ , мА | -1,6 | -2,0 | -0,6 | -0,36 | -0,2 |

| Входной ток I 1 ВХ , мА | 0,04 | 0,05 | 0,02 | 0,02 | 0,02 |

| Выходное напряжение U 0 ВЫХ , В | 0,4 | 0,5 | 0,5 | 0,5 | 0,4 |

| Выходное напряжение U 1 ВЫХ , В | 2,4 | 2,7 | 2,7 | 2,7 | 2,5 |

| Коэффициент разветвления по выходу K РАЗ | 10 | 10 | 10 | 20 | 20 |

| Коэффициент объединения по входу K ОБ | 8 | 10 | — | 20 | — |

| Время задержки распространения сигнала t ЗАД.ср | 19 | 4,8 | 3,8 | 20 | 20 |

| Потребляемый ток, мА: | |||||

| I 0 ПОТ (при U 0 ВЫХ ) | 22 | 36 | 10,2 | 4,4 | 3 |

| I 1 ПОТ (при U 1 ВЫХ ) | 8 | 16 | 2,8 | 1,6 | 0,85 |

| Допустимое напряжение помехи, В | 0,4 | 0,3 | 0,3 | 0,3 | 0,4 |

| Напряжение питания, В | 5 | 5 | 5 | 5 | 5 |

| Выходные токи, мА: | |||||

| I 0 ВЫХ | 16 | 20 | 20 | 8 | 4 |

| I 1 ВЫХ | -0,4 | -1 | -1 | -0,4 | -0,4 |

| Средняя потребляемая мощность на элемент, мВт | 10 | 19 | 4 | 2 | 1,2 |

3.3 Эмиттерно-связанная логика

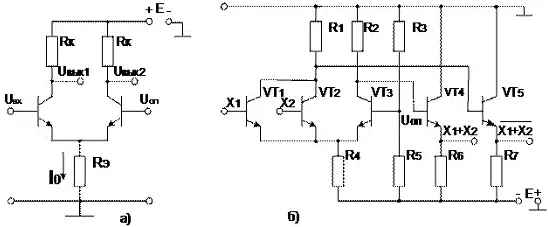

Основой эмиттерно-связанной логики (ЭСЛ) является быстродействующий переключатель тока (Рисунок 14,а). Он состоит из двух транзисторов, в коллекторную цепь которых включены резисторы нагрузки R К, а в цепь эмиттеров обоих транзисторов — общий резистор Rэ, по величине значительно больший Rк. На вход одного из транзисторов подаётся входной сигнал U вх, а на вход другого — опорное напряжение U оп. Схема симметрична, поэтому в исходном состоянии (U вх=U оп) и через оба транзистора протекают одинаковые токи. Через сопротивление Rэ протекает общий ток I О.

Рисунок 14 Эмиттерно-связанная логика: а) переключатель тока;

б) упрощенная принципиальная схема

При увеличении U вх ток через транзистор VT1 увеличивается, возрастает падение напряжения на сопротивлении R э, транзистор VT2 подзакрывается и ток через него уменьшается. При входном напряжении, равном уровню лог «1» ( U вх=U 1), транзистор VT2 закрывается и весь ток протекает через транзистор VT1. Параметры схемы и ток I 0выбираются таким образом, чтобы транзистор VT1 в открытом состоянии работал в линейном режиме на границе области насыщения.

При уменьшении U вх до уровня лог. «0» ( U вх = U 0), наоборот, транзистор VT1 закрыт, а транзистор VT2 находится в линейном режиме на границе с областью насыщения.

В схеме ЭСЛ (Рисунок 14,б) параллельно транзистору VT1 включается ещё один или несколько транзисторов (в зависимости от коэффициента объединения по входу), которые составляют одно из плеч переключателя тока. К выходам ЛЭ для повышения нагрузочной способности подключены два эмиттерных повторителя VT4 и VT5.

При подаче на все входы или на один из них, например, первый, сигнала U ВХ 1= U 1, транзистор VT1 открывается и через него протекает ток I 0, а транзистор VT3 закрывается.

U ВЫХ 1= U 1– U БЭ.нас = U 0

U ВЫХ 2= U ПИТ– U БЭ.нас = U 1

Таким образом, по первому выходу данная схема реализует логическую операцию ИЛИ-НЕ, а по второму — операцию ИЛИ. Нетрудно видеть, что пороговое напряжение U ПОР=U ОП , логический перепад Δ U = U 1- U 0= U БЭ.нас и помехоустойчивость схемы U + ПОМ = U - ПОМ =0,5 U БЭ.нас .

Читать дальшеИнтервал:

Закладка: