Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей

- Название:OrCAD PSpice. Анализ электрических цепей

- Автор:

- Жанр:

- Издательство:ДМК Пресс, Питер

- Год:2008

- Город:Москва, Санкт-Петербург

- ISBN:978-5-9706-0009-2

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Дж. Кеоун - OrCAD PSpice. Анализ электрических цепей краткое содержание

Это руководство по работе в программе OrCAD Pspice предназначено для всех, кто знаком с основными разделами электротехники. При постепенном усложнении задач объясняются все необходимые аспекты работы в OrCAD Pspice, что позволяет творчески применять их при дальнейшем анализе электрических и электронных схем и устройств. Рассмотрение материала начинается с анализа цепей постоянного тока, продолжается анализом цепей переменного тока, затем переходит к различным разделам полупроводниковой электроники. Информация изложена таким образом, чтобы каждый, кто изучал или изучает определенный раздел электротехники, мог сразу же использовать OrCAD Pspice на практике. Больше внимания, чем в других книгах по этой теме, уделяется созданию собственных моделей и использованию встроенных моделей схем в OrCAD Pspice.

На прилагаемом к книге DVD вы найдете демонстрационную версию программы OrCAD PSpice Student Edition 9, которой можно пользоваться свободно. Кроме того, на диске размещена версия OrCAD 10.5 Demo Release, с которой можно работать в течение 30 дней после установки на компьютер.

OrCAD PSpice. Анализ электрических цепей - читать онлайн бесплатно ознакомительный отрывок

Интервал:

Закладка:

VTO -3

BETA 200.000000E-06

RD 10

RS 10

VDD I(RD) I(RS) I(RG)

1.800E+01 9.915E-04 9.915E-04 1.006E-11

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 5.029E-06 ( 2) .7635 ( 3) 9.2744 ( 4) 18.0000

( 1a) 0.0000

VOLTAGE SOURCE CURRENTS

NAME CURRENT

VDD -9.915E-04

vi 0.000E+00

TOTAL POWER DISSIPATION 1.78E-02 WATTS

**** JFETS

NAME JFET

MODEL JM

ID 9.92E-04

VGS -7.63E-01

VDS 8.51E+00

GM 8.91E-04

GDS 0.00E+00

CGS 0.00E+00

CGD 0.00E+00

**** AC ANALYSIS TEMPERATURE = 27.000 DEG С

FREQ I(RD) V(3) V(1) V(2)

5.000E+03 8.828E-07 7.768Е-03 1.000Е-03 1.873E-06

Рис. 11.8. Выходной файл с результатами анализа схемы на рис. 11.7

Временные диаграммы усилителей

Чтобы получить временные диаграммы синусоидального входного напряжения и напряжения на стоке, необходимо несколько изменить входной файл. Входное напряжение задается синусоидальной функцией

vi 1a 0 sin (0 1mV 5kHz)

Анализ переходных процессов выполняется с помощью команды

.TRAN 0.02ms 0.6ms

которая при частоте 5 кГц предусматривает анализ на протяжении трех периодов колебаний.

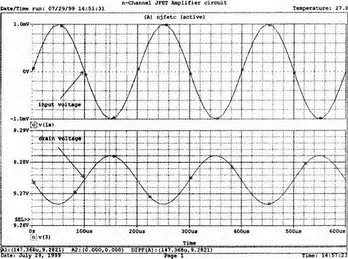

Проведите моделирование и по результатам в Probe убедитесь, что напряжение стока имеет максимальное значение 9,282 мВ и минимальное — 9,266 мВ. Это дает размах напряжения в 15,4 мВ и максимальное значение 7,7 мВ. Результаты близки к полученным ранее расчетным данным. Временные диаграммы показаны на рис. 11.9. Обратите внимание, что курсор расположен так, чтобы показать максимальное значение V(3). При этом входное напряжение находится в соответствующем минимуме.

Рис. 11.9. Временные диаграммы входного и выходного напряжений

В выходном файле (рис. 11.10) показана модификация входного файла, позволяющая включить наряду с анализом переходных процессов еще и гармонический анализ для выходного напряжения V(3). Выходной файл показывает постоянную составляющую напряжения на истоке в 9,274 В. Вторая и более высокие гармоники имеют незначительную величину, давая общее гармоническое искажение менее 1%.

n-Channel JFET Amplifier circuit

VDD 4 0 18V

vi 1a 0 sin(0 1mV 5kHz)

Cb 1a 1 15uF

Cs 2 0 15uF

RG 1 0 0.5MEG

RS 2 0 770

RD 4 3 8.8k

JFET 3 1 2 JM

.MODEL JM NJF(RD=10 RS=10 VTO=-3V BETA=0.2m)

.DC VDD 16V 18V 18V

.OP

.OPT nopage nomod

.TRAN 0.02ms 0.6ms

.PROBE

.FOUR 5kHz V(3)

.END

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 5.029E-06 ( 2) .7635 ( 3) 9.2744 ( 4) 18.0000

( 1a) 0.0000

VOLTAGE SOURCE CURRENTS

NAME CURRENT

VDD -9.915E-04

vi 0.000E+00

TOTAL POWER DISSIPATION 1.78E-02 WATTS

VOLTAGE SOURCE CURRENTS

NAME CURRENT

VDD -9.915E-04

vi 0.000E+00

TOTAL POWER DISSIPATION 1.78E-02 WATTS

**** FOURIER ANALYSIS TEMPERATURE = 27.000 DEG С

FOURIER COMPONENTS OF TRANSIENT RESPONSE V(3)

DC COMPONENT = 9.274381E+00

HARMONIC FREQUENCY FOURIER NORMALIZED PHASE NORMALIZED

NO (HZ) COMPONENT COMPONENT (DEG) PHASE (DEG)

1 5.000E+03 7.679E-03 1.000E+00 -1.797E+02 0.000E+00

2 1.000E+04 2.155E-05 2.806E-03 -1.014E+02 7.829E+01

3 1.500E+04 2.311E-05 3.009E-03 -1.076E+02 7.208E+01

4 2.000E+04 2.231E-05 2.905E-03 -1.139E+02 6.578E+01

5 2.500E+04 2.154E-05 2.805E-03 -1.189Е+02 6.079E+01

6 3.000E+04 2.067E-05 2.692E-03 -1.247E+02 5.507E+01

7 3.500E+04 1.949E-05 2.538E-03 -1.300E+02 4.974E+01

8 4.000E+04 1.848E-05 2.406E-03 -1.352E+02 4.449E+01

9 4.500E+04 1.723E-05 2.244E-03 -1.399E+02 3.983E+01

TOTAL HARMONIC DISTORTION = 7.599231E-01 PERCENT

Рис. 11.10. Выходной файл результатов анализа схемы на рис. 11.7, дополненный результатами спектрального анализа

Мощные полевые транзисторы MOSFET

Для изучения случая, касающегося МОП-транзисторов, необходимо выбрать соответствующую модель такого устройства из библиотеки EVAL.LIB. Это модель IRF150, которая отображает мощный МОП-транзистор n-типа. Чтобы познакомиться с его свойствами, рассмотрим семейства входных и выходных характеристик.

Выходные характеристики

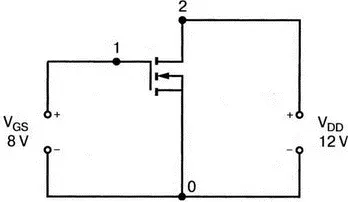

Чтобы получить выходные характеристики, используем схему, показанную на рис. 11.11. Входной файл для нее:

n-Channel MOSFET Output Characteristics

VDD 2 0 12V

VGS 1 0 0VMFET 2 10 0 IRF150; сток, исток, затвор и подложка

.DC VDD 0 12V 0.8V VGS 0 8V 1V

.LIB EVAL.LIB

.PROBE

.END

Рис. 11.11. Схема для снятия характеристик МОП-транзисторов

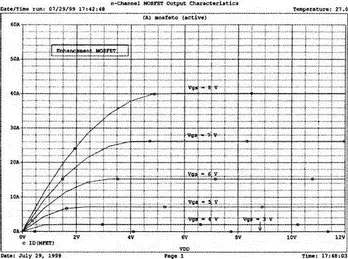

Как показано на рис. 11.11, источник и подложка объединены, как и требуется. Выходные характеристики показаны на рис. 11.12. В качестве примера больших токов стока отметим, что при V GS= 5 В ток насыщения становится больше 7 А. Входной файл библиотечной модели для IRF150 задает пороговое значение напряжения при нулевом смещении V t0=2,831 В. Для n-канального устройства это напряжение является положительным.

Рис. 11.12. Выходные характеристики МОП-транзистора

Входные характеристики

Для входных характеристик несколько значений V DD будут использоваться, как показано в следующем файле:

Input Characteristic for MOSFET

VGS 1 0 0V

VDD 2 0 10V

MOS 2 10 0 IRF150

.DC VGS 0 8V 0.1V VDD 2V 10V 4V .PROBE

.LIB EVAL.LIB

.END

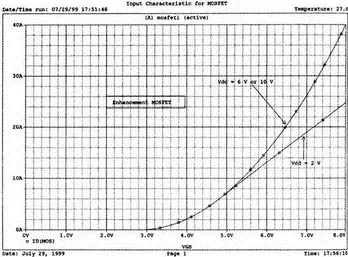

Полученный в результате график показан на рис. 11.13. Из него видно, что пороговое значение V GS немного ниже 3 В и что характеристики при V DD =6 В или больше сливаются в одну кривую.

Рис. 11.13. Входные характеристики МОП-транзистора

Усилители на MOSFET

Усилитель мощности, использующий IRF150, показан на рис. 11.14. Так как используется режим с большими токами истока и стока, значения R d и R s составляют 2 и 0,5 Ом соответственно. Резисторы R 1и R 2образуют делитель напряжения, обеспечивающий значение V GS =4,7 В. При этом входной файл имеет вид:

n-Channel Power MOSFET Amplifier

VDD 4 0 18V

vi 1 0 ac 0.5V

R1 4 2 330k

R2 2 0 220k

Rd 4 3 2

Rs 5 0 0.5

Cb 1 2 15uF

Cs 5 0 15uF

MFET 3 2 5 5 IRF150

.DC VDD 12V 12V 12V .OP

.OPT nopage

.PRINT DC I(RD) I(R1) I(R2) I(RS)

.ac Lin 1 5kHz 5kHz

.PRINT ac i (Rd) v(2) v(3)

.LIB EVAL.LIB

.END

Рис. 11.14. Усилитель мощности на МОП-транзисторе

Выходной файл показан на рис. 11.15. Приведены постоянные и переменные составляющие. Среди постоянных составляющих показаны ток стока (и истока) I D= 1,781 А, напряжения на стоке V(3)=7,827 В и на истоке V(5)=2,543 В.

Читать дальшеИнтервал:

Закладка: