Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

Поскольку регистры I и L содержат беззнаковые числа, два старших разряда шины данных заполняются при чтении этих регистров нулями. Регистры модификации M хранят числа со знаком, поэтому старшие два разряда шины данных дополняются знаковым расширением при их чтении.

Логическое устройство инвертирования разрядов адреса предназначено для вычислений БПФ, когда разряды двоичных значений данных вводятся или генерируются в обратном порядке. Постановка разрядов в обратном порядке возможна только для адресов, генерируемых DAG1. Точкой поворота является средняя точка 14-разрядного адреса, между разрядами 6 и 7, как показано ниже:

Нормальный порядок разрядов:

13 12 11 10 09 08 07 06 05 04 03 02 01 00.

Реверсный порядок разрядов:

00 01 02 03 04 05 06 07 08 09 10 11 12 13.

Реверсная адресация разрешается при установке соответствующего бита в регистре состояния режима MSTAT. При разрешении данного режима работы DAG1 разряды всех адресов, сгенерированных с использованием индексных регистров I0–I3, ставятся в обратном порядке на выходе. При этом значения адресов в индексных регистрах хранятся в нормальном порядке, а преобразование адреса происходит только при выводе на шину адреса. Этот режим сохраняется до сброса соответствующего бита состояния MSTAT.

В DAG1 можно также инвертировать значения адресов с разрядностью менее 14 бит. Для этого необходимо определить первый адрес и записать при инициализации в регистр модификации M значение, вычисляемое для модификации инвертированного выходного значения регистра I в нужном интервале. Это значение равно 214-N, где N - число разрядов, которое необходимо поставить в обратном порядке.

Поскольку генераторы адресов используются для формирования адресов данных, эти устройства используются в командах пересылки данных. Ниже приводится полный список команд пересылки данных в соответствии с принятыми ранее условными обозначениями. Назначение команд приводится в тексте описания этих команд.

Чтение из памяти данных (косвенная адресация):

dreg = DM(|I0|,|M0|);

|I1|,|M1|

|I2|,|M2|

|I3|,|M3|

|I4|,|M4|

|I5|,|M5|

|I6|,|M6|

|I7|,|M7|

Чтение из памяти программ (косвенная адресация):

dreg = PM(|I4|,|M4|);

|I5|,|M5|

|I6|,|M6|

|I7|,|M7|

Запись в память данных (косвенная адресация):

DM(|I0|,|M0|) = dreg;

|I1|,|M1|

|I2|,|M2|

|I3|,|M3|

|I4|,|M4|

|I5|,|M5|

|I6|,|M6|

|I7|,|M7|

Запись в память программ (косвенная адресация):

PM(|I4|,|M4|) = dreg;

|I5|,|M5|

|I6|,|M6|

|I7|,|M7|

Запись в память данных (прямая адресация):

DM() = reg;

Запись содержимого регистров оверлеев в память данных:

DM() = DMOVLAY;

Запись в область ввода/вывода (прямая адресация):

IO() = dreg;

Пересылка регистр-регистр:

reg = reg;

Непосредственная загрузка регистра:

reg = ;

dreg = ;

Чтение регистра оверлеев:

dreg = DMOVLAY;

Запись в регистр оверлеев:

DMOVLAY = dreg;

Чтение из памяти данных (прямая адресация):

reg = DM ();

Чтение из памяти ввода/вывода (прямая адресация):

dreg = IO();

Символьная запись для команд ввода/вывода может принимать значения адреса в диапазоне от 0 до 2048, а для команд обращения к памяти данных от 0 до 16383 (0x3FFF).

Вместо записи dreg могут быть использованы регистры: AX0, АХ1, AY0, AY1, AR, MX0, МХ1, MY0, MY1, MR0, MR1, MR2, SI, SE, SR0, SR1.

Вместо записи reg могут быть использованы все регистры dreg и регистры: I0–I7, M0–M7, L0–L7, TX0, ТХ1, RX0, RX1, SB, PX, ASTAT, MSTAT, SSTAT(только чтение), IMASK, ICNTL, IFC (только запись), CNTR, OWRCNTR (только запись).

Примеры команд пересылки данных:

AX0=АХ1; {Переслать содержимое регистра AX1 в AX0}

AY0=0xA37F; {Загрузить в регистр 16-разрядное число 0xA37F}

AY0=DM(1247); {Прочесть данные из ячейки памяти с адресом 1247 в регистр AY0}

PM(I7, M7) = AX0; {Записать в память программ значение регистра AX0,

используя индексные регистры I7 и M7}

Ниже приведен пример подпрограммы реверсирования разрядов адреса. Данная программа служит для размещения данных по адресам, в которых изменен нормальный порядок разрядов на обратный порядок.

.MODULE scram;

{

Вход: Буфер данных input

Выход: Буфер данных output

Используемые регистры: I0, I4, M0, М4, AY1

}

.CONST N=1025, mv=H#0010; {Инициализация констант mv=16384/N}

.EXTERNAL input, output;

.ENTRY scramble;

scramble: I4=^input; {I4 присвоить адрес начала буфера входных данных}

I0=^output; {I0 присвоить адрес начала буфера выходных данных}

M4=1;

M0=mv; {M0=модификатор для реверса}

L4=0; {Линейные буферы}

L0=0;

ENA BIT_REV; {Разрешение инвертирования разрядов}

CNTR=N;

DO Met UNTIL СЕ; {Организация цикла}

AY1 =DM(I4,M4); {Чтение последовательно организованных данных}

Met: DM(I0,M0)=AY1; {Запись данных в ячейки в обратном порядке}

DIS BIT_REV; {Запрещение инвертирования разрядов}

RTS; {Возврат в вызывающую программу}

.ENDMOD;

Глава 20. Таймер

В этой главе говорится об устройстве таймера сигнального процессора и его назначении.

Кроме рассмотренных нами вычислительных устройств, сигнальный процессор содержит в своем составе программируемый таймер, обеспечивающий автоматический отсчет времени, и два программируемых последовательных порта для связи с внешней периферией. Рассмотрим поочередно эти устройства.

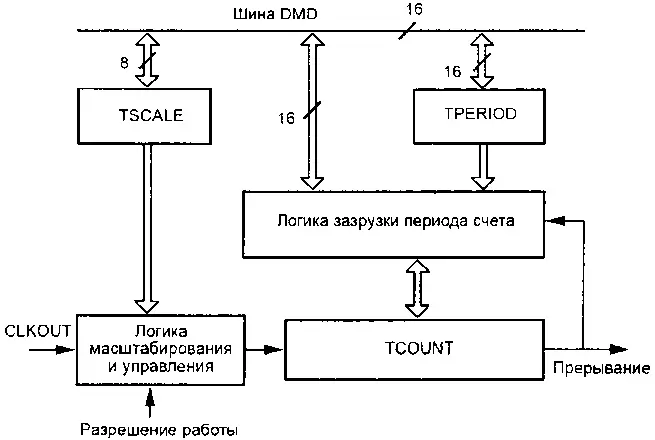

Программируемый таймер сигнального процессора позволяет циклически генерировать прерывания через определенные промежутки времени, кратные циклам процессора. Структурная схема таймера представлена на рис. 20.1.

Рис. 20.1. Структурная схема таймера

Как видно из рисунка, таймер включает в себя 16-разрядный регистр периода TPERIOD, 8-разрядный регистр масштабирования TSCALE, 16-разрядный регистр-счетчик TCOUNT и логику управления. Все три регистра отображены на область памяти данных процессора в соответствии с табл. 20.1.

Таблица 20.1 Формат регистров таймера, отображенных на память данных процессора

| Разряды регистров | Адрес | |||||||

|---|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | |

| TPERIOD | 0x3FFD | |||||||

| TCOUNT | 0x3FFC | |||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0x3FFB |

| Разряды регистров | Адрес | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| TPERIOD | 0x3FFD | |||||||

| TCOUNT | 0x3FFC | |||||||

| TSCALE | 0x3FFB |

Разрешение работы таймера производится установкой в единицу 5-го разряда регистра состояния процессора MSTAT. Когда работа таймера разрешена, регистр-счетчик TCOUNT декрементируется сигналами от логики масштабирования. При достижении счетчиком нуля, формируется прерывание таймера для процессора. После чего в регистр-счетчик TCOUNT автоматически загружается значение регистра периода TPERIOD и работа таймера продолжается.

Читать дальшеИнтервал:

Закладка: