Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Название:Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++

- Автор:

- Жанр:

- Издательство:Горячая линия — Телеком

- Год:2007

- Город:Москва

- ISBN:5-93517-342-5

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Олег Вальпа - Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ краткое содержание

Книга предназначена для самостоятельного изучения и применения на практике цифровых сигнальных процессоров DSP (Digital Signal Processor). На примере популярной микросхемы ADSP2181 фирмы Analog Devices рассмотрены устройство, архитектура и технические характеристики цифрового сигнального процессора. Приведено описание вычислительных блоков процессора, средств разработки программного обеспечения, языка программирования и системы команд процессора. Разработанные автором книги практические схемы с применением сигнального процессора, исходные тексты программ и схемы вспомогательных устройств, полезных при отладке программ для процессора помогут получить необходимые практические навыки, с помощью которых читатель легко освоит другие типы сигнальных процессоров. На прилагаемом к книге диске находятся исходные тексты и исполняемые файлы программ, а так же некоторые полезные утилиты и средства разработки программного обеспечения для сигнальных процессоров.

Для специалистов в области разработки цифровой электронной аппаратуры, будет полезна студентам и аспирантам.

Разработка устройств на основе цифровых сигнальных процессоров фирмы Analog Devices с использованием Visual DSP++ - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

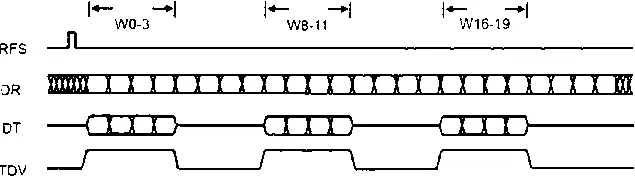

Рис. 21.15. Пример диаграммы работы SPORT0 в многоканальном режиме

Рассмотрим пример программного конфигурирования обоих последовательных портов сигнального процессора, приведенный ниже.

{ ============================= SPORT0 ============================= }

{ Регистры разрешения мультиканального приема/передачи данных SPORT0 }

{ Регистр разрешения приема SPORT0_RX_Channels1 = 0x3ffa }

{ Биты: FEDCBA9876543210 0-игнорирован 1-доступен }

{ Каналы: 3322222222211111 }

{ 1098765432109876 }

ax0 = b#0000000000000000; DM(SPORT0_RX_Channels1) = ax0;

{ Регистр разрешения приема SPORT0_RX_Channels0 = 0x3ff9 }

{ Биты: FEDCBA9876543210 0-игнорирован 1-доступен }

{ Каналы: 111111 }

{ 5432109876543210 }

ax0 = b#0000000000000010; DM(SPORT0_RX_Channels0) = ax0;

{ Регистр разрешения передачи SPORT0_TX_Channels1 = 0x3ff8 }

{ Биты: FEDCBA9876543210 0-игнорирован 1-доступен }

{ Каналы: 3322222222211111 }

{ 1098765432109876 }

ax0 = b#0000000000000000; DM(SPORT0_TX_Channels1) = ax0;

{ Регистр разрешения передачи SPORT0_TX_Channels0 = 0x3ff7 }

{ Биты: FEDCBA9876543210 0-игнорирован 1-доступен }

{ Каналы: 111111 }

{ 5432109876543210 }

ax0 = b#0000000000000011; DM(SPORT0_TX_Channels0) = ax0;

{ Регистр SPORT0_Control_Reg = 0x3FF6 (Регистр управления SPORT0) }

{ Биты: FEDCBA9876543210 }

{ Исх.сост: 0000000000000000 }

ax0 = b#1100011100110111; DM(SPORT0_Control_Reg) = ax0;

{ Регистр SPORT0_SCLKDIV = 0x3FF5 (Модуль деления последов. такт. импульсов) }

{ частота CLKOUT внутренняя удвоенная частота процессора }

{ SCLKDIV = ------------------------------------------------------ - 1; }

{(кадр.с.и.) 2*(частота SCLK синхронизация бит порта) }

{ }

{ SCLKDIV =(( 2*16384КГц ) / ( 2*2048КГц )) -1=8-1=7 }

ax0 = 7; DM(SPORT0.SCLKDIV) = ax0;

{Регистр SPORT0_RFSDIV = 0x3FF4 (Модуль деления последоват. такт. импульсов) }

{ частота SCLK }

{ RFSDIV = ------------ - 1; }

{ частота RFC }

{ RFSDIV = 2048КГц / 8КГц - 1 = 256-1 = 255 }

ax0 = 255; DM(SPORT0_RFSDIV) = ах0;

{Регистр SPORT0_Autobuf = 0x3FF3 (Регистр управления автобуферизацией SPORT0)}

{ Биты: FEDCBA9876543210 }

{ Исх.сост: 0000XXXXXXXXXX00 }

ax0 = b#0000011110101011; DM(SPORT0_Autobuf) = ах0;

{ Регистр SPORT1_Control_Reg = 0x3ff2 (Регистр управления SPORT1) }

{ Биты: FEDCBA9876543210 }

{ Исх.сост: 0000000000000000 }

ax0 = b#0111101001001001; DM(SPORT1_Control_Reg) = ах0;

{Регистр SPORT1_SCLKDIV = 0x3FF1 (Модуль деления последоват. такт. импульсов)}

{ частота CLKOUT внутренняя удвоенная частота процессора }

{ SCLKDIV = ------------------------------------------------------ - 1; }

{(кадр.с.и.) 2*(частота SCLK синхронизация бит порта) }

{ }

{ SCLKDIV = (( 2 *16384КГц ) / ( 2*115200 Гц )) -1 = 142-1 = 852 }

ax0 = 141; DM(SPORT1_SCLKDIV) = ax0; { 115200 бод }

{ Регистр SPORT1_RFSDIV = 0x3FF0 (Модуль деления последоват. такт, импульсов)}

{ частота SCLK }

{ RFSDIV = ------------ - 1; (или число бит в пакете -1) }

{ частота RFC }

{ RFSDIV = 19200 Гц / 1920 Гц - 1 = 10-1 = 9 }

ax0 = 9; DM(SPORT1_RFSDIV) = ax0;

{Регистр SPORT1_Autobuf = 0x3FEF (Регистр управления автобуферизацией SPORT1)}

{ Биты: FEDCBA9876543210 }

{ Исх.сост: 0000XXXXXXXXXX00 }

ax0 = b#0000000000000000; DM(SPORT1_Autobuf) = ax0;

В первых двух блоках программы разрешается работа первого канала приемника SPORT0. В следующих двух блоках программы разрешается работа нулевого и первого канала передатчика SPORT0. Далее в регистр SPORT0_Control_Reg заносится информация о длине слова, формате данных, выравнивании слова, типе компандирования, инвертировании кадровых импульсов и др. режимов работы порта. После чего вычисляется коэффициент деления для тактовой частоты синхронизации SCLK и записывается в регистр SPORT0_SCLKDIV. Аналогично, в следующем блоке программы, производится вычисление коэффициента деления для тактовой частоты кадровых импульсов и запись этого значения в регистр SPORT0_RFSDIV. Завершается конфигурирование SPORT0 записью режима работы порта в регистр управления автобуферизацией SPORT0_Autobuf. Аналогично производится конфигурирование порта SPORT1.

Прием и передача данных через порты могут осуществляться с помощью регистров передатчика TX0, TX1 и регистров приемника RX0, RX1 в портах SPORT0 и SPORT1 соответственно. Эти регистры не отображены в карте памяти процессора, но распознаются мнемоникой ассемблера. Доступ к этим регистрам обеспечивается в произвольный момент во время выполнения программы. Например, следующая команда записывает данные из регистра AX0 в регистр передатчика SPORT1:

TX1 = AX0; {Содержимое регистра AX0 передается в порт SPORT1}

Естественно, что перед этим SPORT1 должен быть программно сконфигурирован ранее описанными командами.

Следующая команда запишет принятые данные из регистра приемника порта SPORT0 в регистр AX0:

AX0 = RX0; {Содержимое регистра приема SPORT0 записывается в регистр AX0}

Часть IV. Среда разработки Visual DSP++

В этой части книги говорится об установке на компьютер современного средства разработки программ для сигнальных процессоров — программного пакета Visual DSP++, его запуске и работе. Приводятся примеры программ и их отладка в среде разработки. Демонстрируется спектральный анализ сигнала с помощью Visual DSP++. Рассказывается о программировании на Си в данной среде разработки.

Глава 22. Установка

В этой главе говорится об установке на компьютер современного средства разработки программ для сигнальных процессоров — программного пакета Visual DSP++.

После знакомства с архитектурой и аппаратными блоками сигнального процессора, а также с его системой команд и директивами языка программирования, пришло время познакомиться с программами, реализующими различные методы математической обработки с помощью сигнального процессора.

В предыдущих материалах мы рассмотрели средства программирования сигнальных процессоров для операционной системы MS DOS. В настоящее время существует более мощное и современное средство программирования для операционной системы Windows, которое носит название Visual DSP++.

Для знакомства с новыми примерами программ удобнее использовать Visual DSP++, поскольку он имеет интегрированный интерфейс разработчика и обладает мощными средствами визуализации и отладки программ. В этом читатели вскоре смогут убедиться самостоятельно.

Программный пакет Visual DSP++ свободно распространяется фирмой Analog Device со своего сервера в Интернете. Он представляет собой тестовую (trial) версию и может быть загружен по адресу http://www.analog.com/processors/resources/crosscore.

Кроме самого программного пакета, необходимо скачать инсталлятор лицензий и пройти бесплатную регистрацию на сервере для получения лицензии.

Тестовую версию Visual DSP++, кроме Интернета, можно получить в представительстве компании Analog Device, или у официальных дистрибьюторов компании на компакт-диске. Фирма Analog Device периодически создает новые версии Visual DSP++, тем не менее при этом соблюдается совместимость с предыдущими программными продуктами, и интерфейс данного пакета легко узнаваем для любой версии. Поскольку описываемый программный пакет не русифицирован и содержит всю информацию на английском языке, ниже дается методика установки программного пакета Visual DSP++, с целью избавления от ошибок при установке пакета и экономии времени читателей.

Читать дальшеИнтервал:

Закладка: