Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]

- Название:Искусство схемотехники. Том 2 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002338-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредоточивается на тонких аспектах проектирования и применения электронных схем. На русском языке издается в трех томах.

Том 2 содержит сведения о прецизионных схемах и малошумящей аппаратуре, о цифровых схемах, о преобразователях информации, мини- и микроЭВМ и микропроцессорах.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 2 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

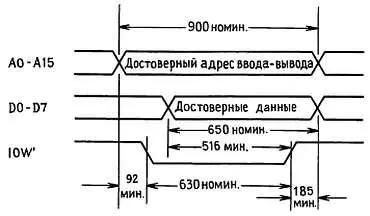

Рис. 10.6. Цикл ввода-вывода при записи (все измерения в нc).

Адрес приемника и данные, которые необходимо передать, выставляются на соответствующие линии магистрали центральным процессором. Строб-сигнал записи (IOW ' или MEMW ' ) устанавливается в низкое состояние цетральным процессором для того, чтобы сигнализировать приемнику о том, что данные установлены и их можно считывать. На магистрали PC адрес гарантированно установлен, начиная с момента времени приблизительно за 100 нс до IOW ' , а данные гарантированно установлены по крайней мере за 500 нс до окончания IOW ' (и в течение следующих 185 нс после окончания этого сигнала).

Для того чтобы принимать участие в подобных играх, периферийное устройство (пусть в нашем случае это — графический дисплей) наблюдает за шинами адреса и данных. Когда устройство обнаруживает свой собственный адрес, оно считывает информацию с шины данных по спаду сигнала IOW ' . Вот и все.

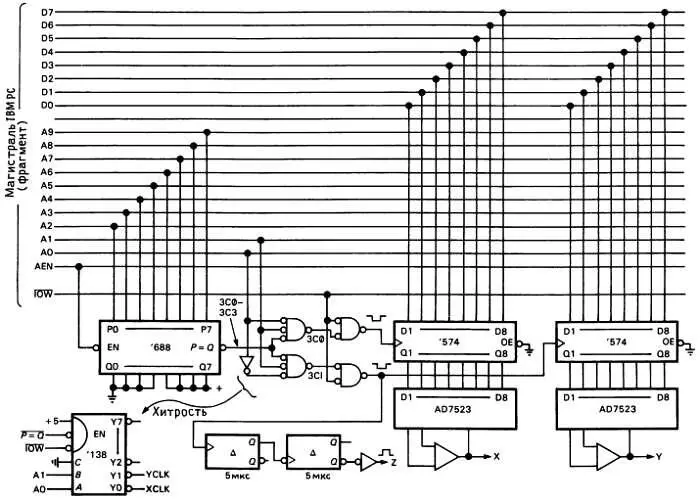

Рассмотрим пример, приведенный на рис. 10.7.

Рис. 10.7. Растровый дисплей.

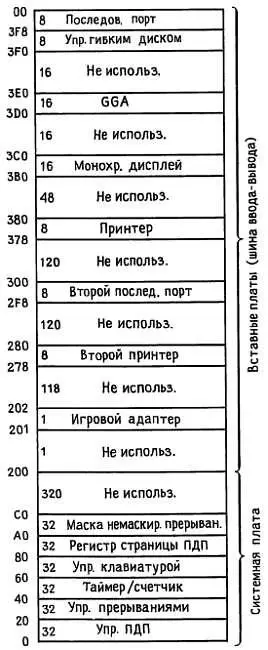

Здесь мы спроектировали растровый графический дисплей; вы последовательно передаете ему пары чисел X, Υ и на его экране отображается каждая точка в декартовой прямоугольной системе координат, причем первое число соответствует абсциссе, а второе — ординате отображаемой точки. Сначала мы должны выбрать адрес устройства ввода-вывода. На рис. 10.8 приведены зарезервированные и доступные адреса устройства ввода-вывода для IBM PC; мы выбираем 3C0H для Х-регистра и ЗС1Н для Y-peгистра.

Рис. 10.8. Адреса ввода-вывода IBM PC.

Микросхема `688-8-разрядный компаратор со стробированием; состоянию равенства сравниваемых кодов которого соответствует низкий уровень на выходе, вырабатывает низкий выходной сигнал в том случае, когда 8 бит разрядов А2-А9 совпадают с заданными значениями, в нашем случае - когда адрес на магистрали лежит в диапазоне 3C0H-3С3Н (вы можете использовать комбинационную схему, но компаратор адреса компактнее). Мы также потребуем в соответствии с ранее приведенными разъяснениями, чтобы AEN был низкого уровня. Трехвходовые логические схемы И-НЕ завершают дешифрацию адреса, используя адресные линии А0, А1 для того, чтобы установить низкий уровень на своих выходах отдельно для адресов 3C0H и ЗС1Н (другой способ будет вкратце описан ниже). В конце концов указанные выходы логически перемножаются с IOW ' для того, чтобы получить синхросигнал для Х- и Y-регистров, которые представляют собой 8-разрядные регистры на D-триггерах (микросхемы `574). Эти регистры фиксируют байты с шины данных в тех случаях, когда а) выбран требуемый адрес, б) сигнал AEN — в низком состоянии, в) был выработан сигнал IOW ' . Восьмиразрядные цифро-аналоговые преобразователи (ЦАП) преобразуют считываемые байты в аналоговое напряжение, подаваемое на Х- и Y-входы устройства управления выводом на электронно-лучевую трубку (ЭЛТ) дисплея. Спустя несколько микросекунд после считывания Y-координаты, два одновибратора вырабатывают 5-микросекундный импульс подсветки, увеличивающий интенсивность свечения изображаемой на экране точки (все устройства управления выводом на ЭЛТ имеют для этого вход Z). Для того чтобы изобразить график или набор символов на экране, необходимо последовательно выводить Х- и Y-координаты, повторяя их в одном и том же порядке (сначала X, а затем Y) достаточно быстро, чтобы глаз не видел мерцания.

Микрокомпьютеры достаточно быстры для того, чтобы успевать в цикле отображать на дисплее несколько тысяч точек без раздражающего мерцания. Учитывая, что растровый дисплей — это стандартное устройство микрокомпьютера для вывода изображений, приведенный пример более полезен в качестве модели фотографического графопостроителя сверхвысокого разрешения, использующего 14-разрядный ЦАП и дисплей с микроскопическим размером точек (см. следующее упражнение).

Несколько полезных замечаний:

а) Отметим, что мы подобрали полярность сигналов таким образом, что D-триггеры переключаются по спаду сигналов IOW ' ; это существенно, так как в момент времени, соответствующий фронту этого импульса, данные могут еще не установиться. Для большей надежности следует удостовериться, что временные соотношения сигналов удовлетворяют временам упреждения и удержания схем `574; фактически, однако, для такой медленной, как у IBM PC магистрали трудно заставить схему, подобную описываемой, работать правильно, поскольку с момента установки данных до спада IOW' проходит более 500 нc.

б) Вы можете сэкономить несколько логических элементов, использовав в цепи дешифрации адреса стробируемый дешифратор так, как показано на рисунке. Дешифраторы типа ,138 (3 разряда на 8 направлений) и типа `139 (сдвоенный, 2 разряда на 4 направления) имеют один или более стробирующих входов и удобны для построения схем такого рода.

в) Отметим также, что мы могли бы объединить 3-входовые и 2-входовые элементы И-НЕ в 4-входовые И-НЕ, здесь этого не сделано для того, чтобы четче выделить отдельно факт дешифрации адреса и затем — совпадения результата дешифрации со строб-сигналом IOW ' .

г) На самом деле мы можем полностью игнорировать разряд А1 и схема будет работать по-прежнему! Однако тогда она начнет откликаться также на адреса 3С2 и 3С3 (как X и Y, соответственно) и произойдет потеря двух адресов ввода-вывода. На практике, однако, часто идут этим путем и, не полностью дешифруя адрес, экономят микросхемы (ведь адресное пространство остается достаточно обширным, даже если вы и потеряете таким образом некоторое количество адресов). В рассматриваемом примере мы можем подключить IOW ' вместо А1 и полностью отказаться от 2-входовой схемы И-НЕ.

д) Сопряжение с магистралью, подобное обсуждаемому, будет более гибким, если адрес устанавливать DIP-переключателями (или DIP-перемычками); тогда вы сможете выбрать адрес верно, чтобы не было конфликта с адресом другого устройства, подключенного к той же магистрали. Внести соответствующие изменения в схему несложно-достаточно восемь входов компаратора подсоединить через ключи к общему проводнику («земле»), а через резисторы — к цепи +5 В.

е) Для пояснения существа дела в этом примере мы использовали отдельные микросхемы 8-разрядных регистров и ЦАПов. На практике у вас есть возможность применить ЦАП со встроенной схемой выборки адреса (например, «микропроцессорно-совместимый» ЦАП типа AD 7528-сдвоенный ЦАП с входной схемой выборки адреса); такая схема выпускается даже в счетверенном варианте (AD7226), а также в варианте с двойной буферизацией, двухкаскадной выборкой адреса для каждого ЦАП (счетверенный ЦАП AD 7225).

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]](/books/607006/paul-horovits-iskusstvo-shemotehniki-tom-2-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)