Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]

- Название:Искусство схемотехники. Том 2 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002338-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредоточивается на тонких аспектах проектирования и применения электронных схем. На русском языке издается в трех томах.

Том 2 содержит сведения о прецизионных схемах и малошумящей аппаратуре, о цифровых схемах, о преобразователях информации, мини- и микроЭВМ и микропроцессорах.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 2 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

ПДП в IBM PC.Компьютер IBM PC, который в общем-то прост, поддерживает упрощенный протокол ПДП. На системной плате установлен контроллер ПДП (Intel 8237) со встроенными адресным и байтовым счетчиками, а также дополнительными логическими схемами для блокировки ЦП и перехвата управления магистралью. Таким образом, внешнее устройство, которое хочет выполнить ПДП, не должно вырабатывать адреса и управлять магистралью. Вместо этого он сигнализирует контроллеру с помощью одной из трех DRQ1-DRQ3 линий запроса ПДП; контроллер откликается по соответствующей линии DACK0-3 ' (подтверждение ПДП). Затем контроллер управляет передачей данных, формируя адрес и соответствующие строб-сигналы, синхронно с формированием внешним устройством данных для передачи в память (или синхронно с приемом данных из памяти). Во всем этом процессе память не замечает ничего необычного, поскольку генерация адресов и строб-сигналов управления памятью (MEMW ' или MEMR ' ), которая обычно поддерживается ЦП, в данном случае поддерживается контроллером 8237 и, если ПДП сопровождает передачу данных в память, данные формируются внешним устройством. С другой стороны внешние устройства «знают» все особенности того, как надо формировать запрос ПДП (и что делать при получении подтверждения посредством сигнала DACK ' ); таким образом, когда контроллер ПДП выставляет сигнал IOR ' (или IOW ' ), внешнее устройство вырабатывает (или принимает) соответствующие байты. Вы можете удивиться, как это такой простодушный, сторонний наблюдатель, как внешнее устройство, не запутается во время ПДП, когда выставлены и строб- сигналы ввода-вывода, и адреса, причем эти адреса являются адресами в памяти, установление которых сопровождается строб-сигналами управления памятью MEMW ' или MEMR ' , генерируемыми контроллером; эти адреса не имеют никакого отношения к портам ввода-вывода.

Секрет здесь заключается в нашем старом знакомом-сигнале AEN, который добавлен к магистрали специально только для решения подобных проблем. Уровень сигнала AEN во время передачи данных в режиме ПДП устанавливается высоким, и функции разрешения адресации всех портов ввода-вывода должны вычисляться как логическое произведение с низким уровнем сигнала AEN для того, чтобы предотвратить ложную реакцию при адресации памяти в режиме ПДП.

Даже при использовании отдельной микросхемы контроллера вам все еще надо задать начальный адрес, количество байтов и направление передачи данных для грядущего режима ПДП. Эти параметры заносятся в контроллер 8237, который обязан иметь набор регистров, куда из ЦП (с помощью программируемого ввода-вывода) можно записать соответствующие значения. Настройка ПДП осуществляется весьма просто (см. книгу Эггбрехта для более детального ознакомления), если не считать того, что, как и у большинства микросхем БИС, здесь также имеется ошеломляющее разнообразие выбора различных режимов работы (посимвольная передача, поблочная передача и т. п.). К счастью IBM PC достаточно примитивна и позволяет вам использовать только режим посимвольной передачи, при котором каждый запрос DRQ сопровождается передачей лишь одного байта. Если вы настаиваете на передаче целого блока данных, поддерживая сигнал DRQ в высоком состоянии, контроллер 8237 освобождает магистраль на один цикл ЦП между циклами ПДП; это позволяет компьютеру сохранять работоспособность даже в том случае, когда у вас такое «прожорливое» внешнее устройство, что оно старается «заграбастать» магистраль полностью.

Стандартная PC обладает довольно скромными возможностями режима ПДП-около 2 мкс на передаваемый байт. По сравнению с количеством прерываний количество каналов ПДП в IBM PC меньше. Для шины ввода-вывода доступны три канала DRQ1-DRQ3 (DRQ0 уже задействован на внутренние нужды — для регенерации динамической памяти): DRQ1 используется жестким диском, а DRQ2 — гибким. На все остальное остается DRQ3.

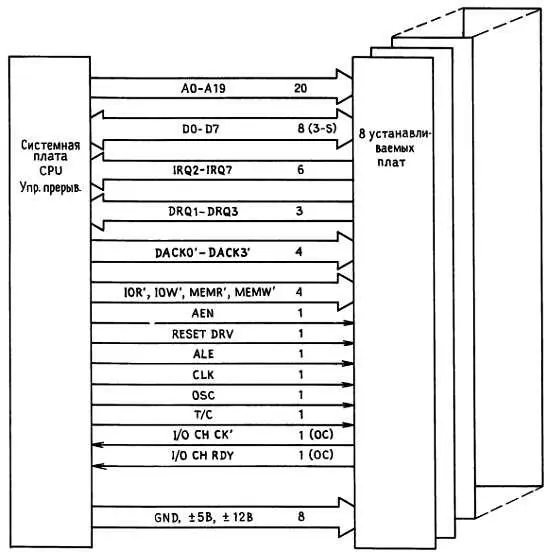

На рассмотренных нами примерах-программируемого ввода-вывода, прерываний, ПДП-мы познакомились с большинством сигналов магистрали, поступающими на плату внешнего устройства IBM PC В табл. 10.1 (и на рис. 10.14) приведен полный перечень сигналов магистрали с цоколевкой разъема. Для полноты изложения ниже описан каждый из этих сигналов, начиная с тех, с которыми мы уже встретились.

Рис. 10.14. Магистраль IBM PC.

А0-А19. Шина адреса. Два состояния, работает только на запись, действующий уровень сигнала-высокий. Все 20 разрядов используются для адресации памяти (совместно с сигналами MEMR ' и MEMW ' , которые играют роль строб-сигналов, по аналогии с сигналами IOR ' и IOW ' ), но только 16 младших разрядов используются при адресации ввода-вывода, (64 К адресов портов); устройства ввода-вывода должны осуществлять выборку адреса только при низком уровне сигнала AEN.

Важное замечание: ввод-вывод в пределах системной платы предусматривает адресацию только десятью младшими разрядами, используя при этом лишь адреса 000H-1FFH, поэтому адреса устройств ввода-вывода должны иметь в своих младших разрядах коды в диапазоне 200H-3FFH. Вы можете поступить умнее, используя наряду со свободными 10-разрядными адресами еще и 6 старших бит, расширив таким образом адресное пространство портов ввода-вывода до 64К.

D0-D7. Шина данных. Три состояния, двунаправленная, действующий уровень сигнала-высокий. Данные выставляются ЦП при записи в память или в порт ввода-вывода: выставляются памятью при чтении из памяти, в том числе и при ПДП; выставляются портом ввода-вывода при чтении из порта, в том числе и в память при ПДП.

IOR ' , IOW ' , MEMR ' , MEMW ' . Строб-сигналы данных . Два состояния являются выходными (по отношению к ЦП), действующий уровень сигнала — низкий. Формируются ЦП при чтении или записи. При записи данные должны быть зафиксированы по спаду (положительному) и при надлежащем адресе; при чтении должны быть выставлены одновременно со строб-сигналом при заданном адресе.

AEN. Разрешение адреса. Два состояния, является выходным (по отношению к ЦП), действующий уровень сигнала — высокий. Вырабатывается ЦП во время циклов ПДП. Порты ввода-вывода не должны дешифровать адрес при наличии сигналов IOR ' , IOW ' , за исключением тех случаев, когда порты ввода-вывода принимают сигнал DACK и используют сигналы IOR ' и IOW ' для стробирования байтов данных ПДПН.

IRQ2-IRQ7. Запрос прерывания. Два состояния, является входным (по отношению к ЦП), действующим является нарастающий фронт. Вырабатывается устройством, запрашивающим прерывания. Приоритеты установлены таким образом, что IRQ2 имеет наивысший, a IRQ7 — наинизший приоритет. Контроллер прерываний 8259 допускает их маскирование, устанавливаемое ЦП посредством записи в порт по адресу 21Н. Каждый уровень IRQ может быть использован одновременно только одним устройством.

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]](/books/607006/paul-horovits-iskusstvo-shemotehniki-tom-2-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)