М. Нсанов - Цифровые устройства. Учебник для колледжей

- Название:Цифровые устройства. Учебник для колледжей

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:9785449318817

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

М. Нсанов - Цифровые устройства. Учебник для колледжей краткое содержание

Цифровые устройства. Учебник для колледжей - читать онлайн бесплатно ознакомительный отрывок

Интервал:

Закладка:

Подобные микросхемы, содержащие объединенные в группы элементы НЕ или повторители с тремя состояниями, которые имеют еще и повышенную нагрузочную способность, называют шинными формирователями или магистральными приемопередатчиками .

П р и м е ч а н и е . Часть линий, сгруппированных по функциональному назначению, называется шиной . Например, информационная шина, по всем линиям которой передается информация; шина управления, по линиям которой передаются сигналы управления; и т. д. Совокупность шин называется магистралью .

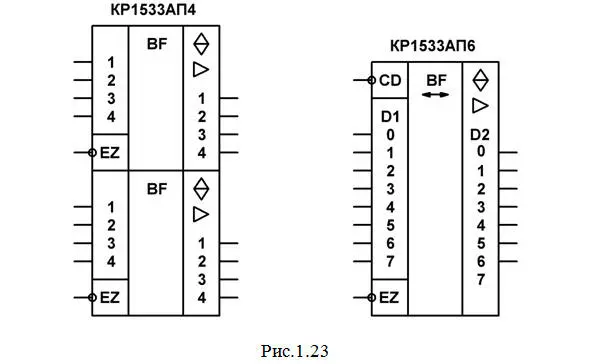

У таких ИМС в третьей части маркировки обычно ставят буквы АП, хотя иногда используется маркировка ЛПили ЛН(как, например, в только что рассмотренной микросхеме). Условное графическое изображение формирователей имеет, как правило, буквы BF(от английского b u f fer – буфер). Применяются они обычно в микропроцессорных системах и системах обработки данных с магистральной организацией обмена информацией.

Можно привести еще один пример шинного формирователя: КР1533АП4 (рис.1.23). Данная ИМС содержит два четырехразрядных магистральных передатчика, каждый из которых имеет по четыре буферных повторителя с тремя состояниями и повышенным коэффициентом разветвления.

Некоторые формирователи могут передавать информацию в обоих направлениях. Например, восьмиразрядный двунаправленный приемопередатчик КР1533АП6 (рис.1.23) содержит 8 буферных повторителя с тремя состояниями и повышенной нагрузочной способностью, у которых изменение направления передачи информации производится с помощью сигнала на дополнительном входе CD: при CD = 1 передача информации производится от D1к D2, при CD = 0 – наоборот.

***1.10. Мажоритарные элементы

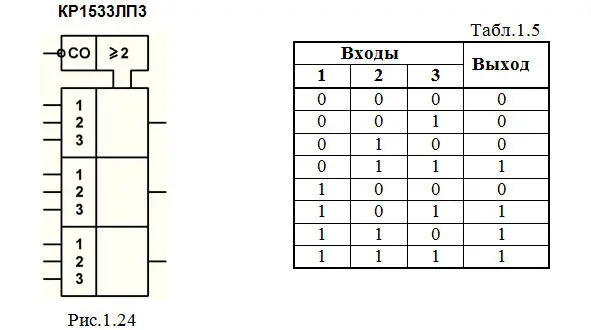

Мажоритарный (от английского majority – большинство) элемент формирует на своем выходе такой сигнал, который действует на большинстве его входов.

В качестве примера можно рассмотреть микросхему КР1533ЛП3 (рис.1.24). Она содержит три мажоритарных элемента «два из трех» (т.е. на выходе формируется такой сигнал, который действует не менее чем на двух входах из трех), работа каждого из них описывается таблицей истинности (табл.1.5).

ИМС имеет общий для трех элементов управляющий вход СО, на котором для нормальной работы должен поддерживаться уровень логического 0. При СО = 1 значение выходного сигнала определяется только сигналом на входе 3. 1 1 ***Темы, отмеченные звездочками, не были включены в программу предмета ко времени работы над книгой из-за недостатка времени по учебным планам. Они здесь даются для расширения и углубления знаний тех учащихся, которым это интересно, а также для помощи при выполнении курсовых работ и дипломных проектов.

1.11. Преобразователи уровней

При использовании в аппаратуре микросхем различной структуры возникает необходимость их согласования по таким важнейшим параметрам, как уровни сигналов и потребляемая мощность.

Эту задачу решают специальные ИМС, которые получили название: преобразователи уровней логических сигналов.

Микросхемы любых преобразователей в третьей группе маркировки имеют первую букву П, а вторая буква указывает на конкретный вид преобразователя. Для ИМС преобразователей уровней принято обозначение: ПУ.

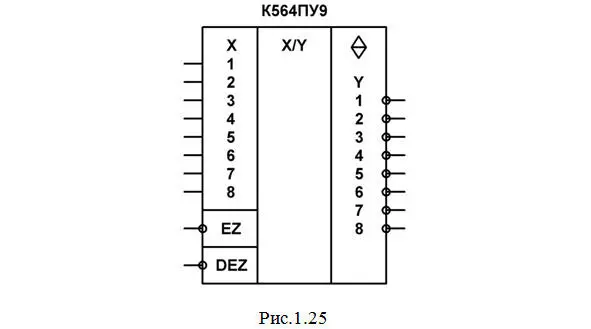

Для примера рассмотрим микросхему К564ПУ9 (рис.1.25).

Она может выполнять одновременное преобразование 8 сигналов как от уровня ТТЛ (ТТЛШ) к МОП, так и от уровня МОП к ТТЛ (ТТЛШ). Входы ЕZи DEZпредназначены для управления режимами работы:

– при подаче на вход DEZсигнала 0 микросхема выполняет преобразование сигналов МОП уровня в ТТЛ (ТТЛШ) при любом сигнале на входе EZ;

– при одновременной установке сигналов 1 на входах EZи DEZмикросхема выполняет преобразование сигналов ТТЛ (ТТЛШ) уровня в МОП;

– если же на входе EZустановить уровень логического 0, а на вход DEZподать 1, то микросхема переходит в Z-состояние.

Следует учесть, что выходные сигналы инвертируются, т.к. на выходах стоит графический знак операции логического отрицания.

П р и м е ч а н и е. В настоящее время выпускаются микросхемы МОП-структуры, прямо совместимые со стандартными сериями ТТЛ (ТТЛШ). Например, микросхемы серий 1564, КР1564, КР1594 (аналоги – соответственно серии ММ54НС, ММ74НС и 74АСТ фирмы «National Semiconductor»).

Раздел 2. Основы синтеза и анализа работы цифровых устройств

Целью тем, изложенных в разделе 2, является овладение учащимися основам синтеза (разработки структуры и построения схем) ЦУ с помощью логических элементов и анализа (проверки правильности) их работы.

2.1. Формы записи логических функций

Предположим, задана таблица истинности (табл.2.1 на рис.2.1), описывающая работу ЦУ, которое имеет три входа Х 1, Х 2, Х 3и один выход Y 1.

Цель: с помощью логических элементов построить схему, которая будет работать так, как указано в этой таблице.

Первым этапом работы является запись зависимости выходной логической функции (значений сигнала на выходе) Y 1от значений логических переменных Х 1, Х 2, Х 3(значений сигналов на входах) в базисе И, ИЛИ, НЕ (т.е. с использованием операций логического умножения, сложения и отрицания). Такая запись может выполняться в двух формах:

1. СДНФ (совершенная дизъюнктивная нормальная форма) представляет собой несколько многочленов (минтермов), объединенных операцией логического сложения (дизъюнкции), почему форма и названа дизъюнктивной. Она составляется для значений функции Y, равных 1 , количество которых и определяет число многочленов. Каждый многочлен представляет собой логическое умножение всех переменных (в данном случае – трех переменных Х 1, Х 2, Х 3), причем для нулевого значения любой переменной следует брать ее инверсию.

Читать дальшеИнтервал:

Закладка: