Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]

- Название:Искусство схемотехники. Том 2 [Изд.4-е]

- Автор:

- Жанр:

- Издательство:Мир

- Год:1993

- Город:Москва

- ISBN:5-03-002338-0 (русск.); 5-03-002336-4; 0-521-37095-7 (англ.)

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е] краткое содержание

Широко известная читателю по предыдущим изданиям монография известных американских специалистов посвящена быстро развивающимся областям электроники. В ней приведены наиболее интересные технические решения, а также анализируются ошибки разработчиков аппаратуры: внимание читателя сосредоточивается на тонких аспектах проектирования и применения электронных схем. На русском языке издается в трех томах.

Том 2 содержит сведения о прецизионных схемах и малошумящей аппаратуре, о цифровых схемах, о преобразователях информации, мини- и микроЭВМ и микропроцессорах.

Для специалистов в области электроники, автоматики, вычислительной техники, а также студентов соответствующих специальностей вузов и техникумов.

Искусство схемотехники. Том 2 [Изд.4-е] - читать онлайн бесплатно полную версию (весь текст целиком)

Интервал:

Закладка:

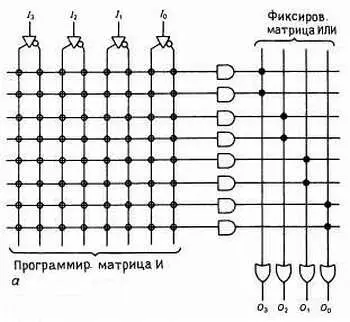

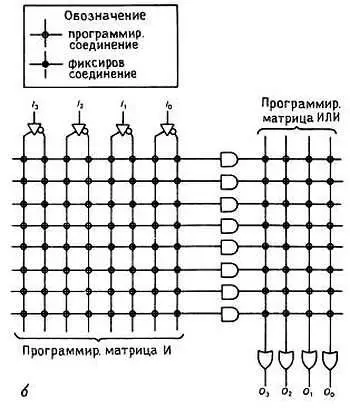

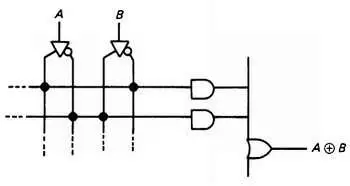

Программируемая логика. ПМЛ (программируемая матричная логика; PAL-товарный знак фирмы Monolitic Memories Inc.) и ПЛМ (программируемые логические матрицы) являются двумя основными видами программируемой логики. Они являются ИС со многими вентилями, связи между которыми могут программироваться (подобно ПЗУ) для формирования желательных логических функций. Они выполняются как в биполярном, так и в КМОП-вариантах, первые используют прожигаемые перемычки (однократно-программируемые), вторые — плавающие вентильные КМОП схемы (ультрафиолетового или электрического стирания). Вы не можете запрограммировать любую связь, какую желаете — вы будете ограничены встроенной структурой. Рис. 8.44 показывает основные схемы комбинационных (не регистровых) ПЛМ и ПМЛ.

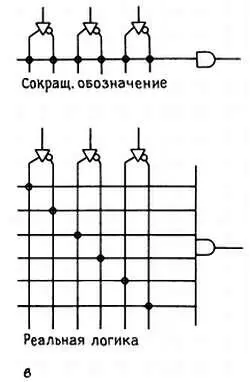

Рис. 8.44.Программируемая логика: а— ПЛМ; б— ПМЛ; в— фрагмент программируемых соединений с многовходовым вентилем И; кружками обозначены плавкие перемычки или другие программируемые соединения.

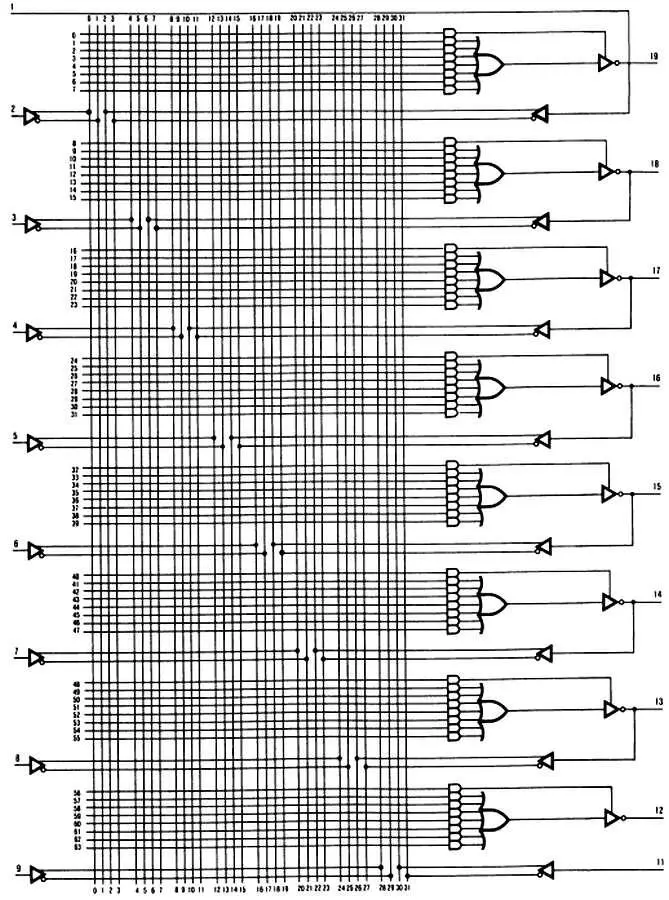

Для простоты на этом рисунке вентили И или ИЛИ нарисованы с одним входом, хотя в действительности они являются много-входовыми вентилями с входом для каждого перекрестия. Каждый выход (с 3 состояниями) комбинационной ПМЛ выводится от вентиля ИЛИ, а каждый вход подсоединяется к вентилю И с дюжинами входов. Например, 16L8 (рис. 8.45) имеет восемь 7-входовых вентилей ИЛИ; каждый возможный сигнал достижим для каждого вентиля И, включая 10 входных контактов (и инверторы для них) и 8-выходных контактов (и инверторы к ним).

Рис. 8.45. Комбинационная ПМЛ 16L8имеет 10 специальных входов, 2 специальных выхода и 6 двунаправленных линии входа/выхода (с 3-м состоянием). «16L8» означает 16 входов (макс), 8 выходов (макс.) (низкий уровень - истинное значение).

(с разрешения фирмы Advanced Micro Devices, Калифорния.)

Разрешение третьего состояния также устанавливается от 32-входового вентиля И. ПЛМ подобна ПМЛ, но обладает большей гибкостью — выходы вентилей И могут связываться со входами вентилей ИЛИ в любой комбинации (т. е. программироваться), что предпочтительней, чем жесткое присоединение, как в ПМЛ.

Заметим, что ПМЛ и ПЛМ, которые мы описывали, являются комбинационными устройствами (т. е. выполнены только на вентилях, без памяти). Другой разновидностью программируемой логики является последовательностная логика, т. е. имеющая память (регистры), подробно мы рассмотрим их в, следующем разделе. Для использования ПМЛ и ПЛМ вы должны иметь программатор, как часть аппаратного обеспечения, который знает, как прожигать перемычки (или другие типы программируемых средств) и проверить окончательный результат. Все программаторы имеют связь через последовательный порт с микрокомпьютером (стандартное средство связи на IBM PC или совместимой с ней), на котором вы работаете с программным обеспечением программатора. Некоторые из современных программаторов включают одноплатный компьютер, который работает с собственным программным обеспечением.

Простейшее программное обеспечение просто позволяет вам выбрать перемычки для прожигания; вы изображаете это в зависимости от того, какую логику вы хотите получить на уровне вентилей, затем перечисляете (или помечаете на графическом дисплее) эти перемычки. Рис. 8.46 показывает простой пример для функции исключающее ИЛИ на два входа на одном из выходов ПМЛ.

Рис. 8.46. Исключающее ИЛИна ПМЛ.

Хорошие программаторы позволяют вам задавать буквы выражения (если они вам известны) или таблицы истинности; программное обеспечение затем делает остальное, включая минимизацию, моделирование и программирование. Хотя ПЛМ более гибкие, фаворитом в современном проектировании являются ПМЛ. Это из-за того, что они быстрее (так как сигнал проходит только через один массив перемычек), дешевле и обычно удовлетворяют задаче. Как мы увидим позже, новые ПМЛ, использующие «макроячейки» и «складную архитектуру» дают вам некоторую дополнительную гибкость в проектировании на ПМЛ с фиксированными ИЛИ-вентилями. Таким образом, ПМЛ представляют собой гибкую и компактную альтернативу ИС с фиксированными функциями и не должны выпадать из виду у серьезного проектировщика схем. Мы покажем, как (и где) применять программируемую логику с использованием полезных хитростей в разд. 8.27 .

Последовательностная логика

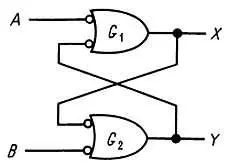

Вся рассмотренная выше цифровая логика строилась на комбинационных схемах (т. е. наборах вентилей), в которых выход полностью определяется текущим состоянием входов. В этих схемах отсутствует «память», отсутствует предыстория. Жизнь цифровой логики станет более интересной, если устройства снабдить памятью. Это дает возможность конструировать счетчики, арифметические регистры и различные «умные» схемы, которые выполнив одну интересную функцию, начинают делать другую. Основным узлом таких схем является триггер, колоритное имя для описания устройств, которые в простейшей форме представлены на рис. 8.47.

Рис. 8.47. RS-триггер.

Предположим, что оба входа А и В имеют высокий уровень. Тогда, в каком состоянии будут выходы X и Y ? Если X будет иметь высокий уровень, то последний будет присутствовать на обоих входах вентиля G 2 , и устанавливать Y в состояние низкого уровня. Это согласуется с состоянием выхода X (высокий уровень), следовательно, все правильно. Не правда ли?

Х = В, Y = H .

Неверно! Схема симметрична, следовательно, правомерно будет и состояние, при котором

Х = Н, Y = B .

Состояние, когда оба выхода X и Y имеют высокий (или низкий) уровень, невозможно (вспомним, что А = В = высокий уровень). Таким образом, триггер имеет два устойчивых состояния (иногда его называют «бистабильной» схемой). В каком из этих двух состояний он окажется, зависит от его предыстории, т. е. он обладает памятью. Для того чтобы в эту память что-то записать, достаточно на один из входов триггера кратковременно подать низкий уровень. Например, после кратковременной подачи низкого уровня на вход А триггер гарантированно установится в состояние

Читать дальшеИнтервал:

Закладка:

![Обложка книги Пауль Хоровиц - Искусство схемотехники. Том 2 [Изд.4-е]](/books/607006/paul-horovits-iskusstvo-shemotehniki-tom-2-izd-4-e.webp)

![Фредерик Браун - Брат гули-бьябона: Рассказы и повести о снежном человеке. Том II [Изд. 3-е, дополненное]](/books/1089189/frederik-braun-brat-guli.webp)