М. Нсанов - Цифровые устройства. Учебник для колледжей

- Название:Цифровые устройства. Учебник для колледжей

- Автор:

- Жанр:

- Издательство:неизвестно

- Год:неизвестен

- ISBN:9785449318817

- Рейтинг:

- Избранное:Добавить в избранное

-

Отзывы:

-

Ваша оценка:

М. Нсанов - Цифровые устройства. Учебник для колледжей краткое содержание

Цифровые устройства. Учебник для колледжей - читать онлайн бесплатно ознакомительный отрывок

Интервал:

Закладка:

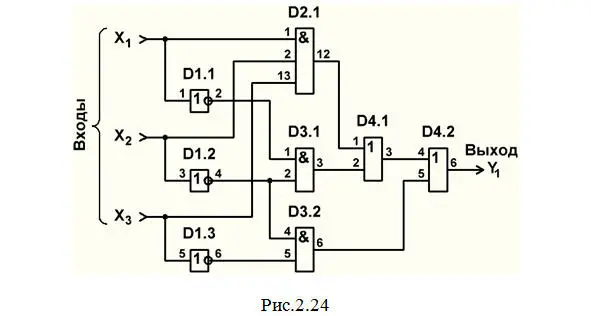

Во второй колонке первым стоит элемент 3Ииз микросхемы КР1533ЛИ3, поэтому ее мы обозначим следующим по порядку номером D2. В указанной микросхеме используется один элемент 3И, который будет иметь обозначение D2.1.

В этой же второй колонке далее стоят два элемент 2Ииз микросхемы КР1533ЛИ1, их мы обозначим D3.1 и D3.2.

Последними в схеме стоят два элемента 2ИЛИиз микросхемы КР1533ЛЛ1, их нужно обозначить D4.1 и D4.2.

Кроме этого, у всех элементов схемы следует указать нумерацию их выводов в корпусе микросхем (смотрите предпоследний абзац темы 1.5 и Приложение 1).

В результате получаем окончательный вариант схемы (рис.2.24).

П р и м е ч а н и я :

– в дальнейшем для достижения учебных целей мы не будем ставить нумерацию выводов корпусов микросхем, чтобы не загромождать чертежи;

– будем оставлять вспомогательные надписи, которые помогут учащимся разбираться в построении схем.

– в реальных чертежах отдельных плат или ТЭЗов (типовых элементов замены) входы и выходы оформляются иначе, чем показано на рис.2.26. Подробнее об этом будет сказано при подготовке к курсовому проектированию, а сейчас пока подписывать входы и выходы будем именно так.

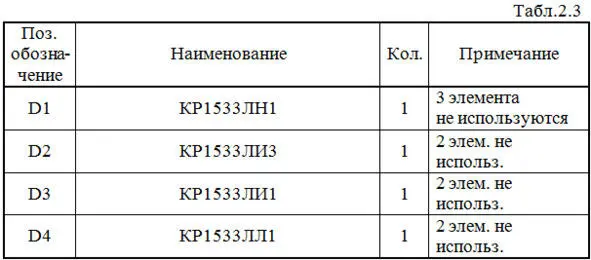

Любая реальная схема дополняется сведениями о всех используемых здесь микросхемах, любых других элементах и устройствах в виде специальной таблицы, которая имеет официальное название «Перечень элементов» (табл.2.3). По стандарту указанная таблица должна помещаться либо на поле чертежа, либо после него.

П р и м е ч а н и я к таблице:

1. Названия заголовков устанавливаются стандартом и их обязательно нужно сокращать именно так, как показано в табл.2.3.

2. Размеры таблицы также устанавливаются стандартом:

– ширина колонок по порядку слева направо: 20 (Позиционное обозначение), 110 (Наименование), 10 (Количество), 45 (Примечание) мм;

– высота строки заголовков – 15 мм;

– высота всех остальных строк – не менее 8 мм.

3. В колонке «Примечание» мы в дальнейшем будем указывать количество элементов из указанной микросхемы, которые в данной схеме использоваться не будут.

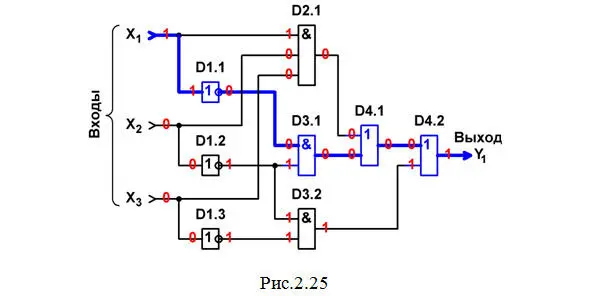

Выполним анализ работы ЦУ хотя бы в одном статическом режиме (рис.2.25). Для этого на входы подадим цифровые сигналы, например: Х 1= 1, Х 2= 0, Х 3= 0. По схеме, последовательно указывая значения сигналов на входах и выходах всех элементов (см. тему 1.2), определяем, что на выходе ЦУ формируется сигнал Y 1= 1. Сравниваем полученный результат с таблицей истинности данного ЦУ (соответствующая строка выделена краснымцветом в табл.2.1) и делаем вывод: в данном случае (при заданных значениях входных сигналов) устройство сработало правильно.

На основании вышеприведенного анализа нельзя сделать вывод о правильности построения данной схемы. Такой вывод будет корректным только в том случае, если выполнить анализ работы ЦУ для всех 8 статических режимов (то есть для всех комбинаций входных сигналов) согласно таблице истинности (см. табл.2.1).

При необходимости анализ работы ЦУ в динамическом режиме производится так, как описано в теме 1.2.

Оценка качества схем в основном производится по двум параметрам: аппаратурным затратам W и задержке T .

Аппаратурные затраты W обычно определяются количеством используемых корпусов микросхем (значение ряда других параметров – потребляемой мощности, надежности и др. – допустимо считать приблизительно пропорциональными W). В данном случае мы берем:

– 3 элемента НЕ из микросхемы КР1533ЛН1, которая содержит в целом 6 элементов; то есть используем 3/6 = 0,5 корпуса ИМС;

– 1 элемент 3Ииз микросхемы КР1533ЛИ3 (здесь всего – 3 элемента), т.е. используем 1/3 = 0,33 корпуса ИМС;

– 2 элемента 2Ииз микросхемы КР1533ЛИ1, содержащей в целом 4 элемента; т.е. используем 2/4 = 0,5 корпуса ИМС;

– 2 элемента 2ИЛИиз микросхемы КР1533ЛЛ1, которая содержит всего 4 элемента; т.е. используем 2/4 = 0,5 корпуса ИМС.

Итого величина аппаратурных затрат получается равной:

W = 0,5 + 0,33 + 0,5 + 0,5 = 1,83 корпуса.

П р и м е ч а н и е: лишние элементы частично занятых корпусов микросхем не учитываются, поскольку они могут быть использованы в других узлах.

Наряду с аппаратурными затратами очень важным критерием качества схем является задержка Т. В схемах, построенных с помощью микросхем средней степени интеграции, задержка достаточно объективно оценивается средним временем задержки распространения сигнала t P(см. §1.6) входящих в нее элементов по максимально длинному пути сигналов от входа к выходу. В рамках одной серии обычно полагают, что задержка любого логического элемента равна некоторой усредненной для данной серии величине τ, которая вместе с t Pнепосредственно элемента включает в себя и приближенную задержку на линиях связи между элементами. Для микросхем серии КР1533 значение τможно принять равным 8 нс.

Рассмотрим все возможные пути прохождения сигналов по схеме (рис.2.14) от входов к выходу и определим соответствующую величину задержки:

– со входа Х 1через 3 элемента – D2.1, D4.1 и D4.2, поэтому

Т = 3τ = 3·8 = 24 нс;

– со входа Х 1через 4 элемента – D1.1, D3.1, D4.1 и D4.2 (этот путь на рис.2.24 выделен жирной синейлинией);

Т = 4τ = 4·8 = 32 нс;

– со входа Х 2через 3 элемента – D2.1, D4.1 и D4.2;

Т = 3τ = 3·8 = 24 нс;

– со входа Х 2через 4 элемента – D1.2, D3.1, D4.1 и D4.2;

Т = 4τ = 4·8 = 32 нс;

– со входа Х 3через 3 элемента – D2.1, D4.1 и D4.2;

Т = 3τ = 3·8 = 24 нс;

– со входа Х 3через 3 элемента – D1.3, D3.2 и D4.2;

Т = 3τ = 3·8 = 24 нс.

Таким образом, для данной схемы максимальная задержка составляет Т = 4τ = 4·8 = 32 нс.

П р и м е ч а н и е. Строго говоря, полученное численное значение (в данном случае 32 нс) особого значения не имеет, так как задержка (да и аппаратурные затраты тоже) используются в основном для сравнительной оценки качества различных вариантов схем одного и того же ЦУ. Кроме этого, схема может строиться не на микросхемах логических элементов, а включаться целиком в состав какой-либо другой микросхемы, что приведет к существенному уменьшению задержки из-за сокращения линий связи между элементами внутри микросхемы, выполненной по интегральной технологии. Поэтому в большинстве случаев достаточно оперировать величиной Т = 4τ, не указывая его численное значение.

Читать дальшеИнтервал:

Закладка: